高性能差分輸出VCXO是什么

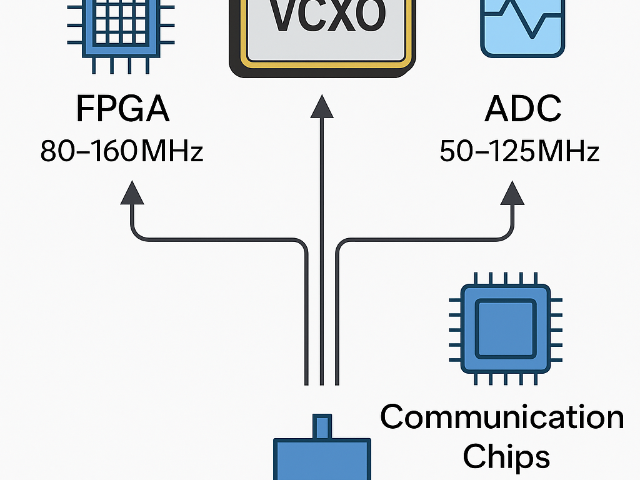

差分輸出VCXO優(yōu)化FPGA SerDes鏈路時(shí)鐘 FPGA內(nèi)置的SerDes模塊是實(shí)現(xiàn)高速串行通信的關(guān)鍵接口,差分時(shí)鐘源是其性能表現(xiàn)的關(guān)鍵,。FCom富士晶振差分輸出VCXO通過精確頻率控制與低相位抖動(dòng),,為FPGA鏈路提供穩(wěn)定的參考時(shí)鐘。 在Xilinx Kintex,、Intel Stratix等系列FPGA中,,TX/RX PLL對時(shí)鐘源的抖動(dòng)容忍度有限。FCom VCXO輸出的LVPECL或LVDS信號(hào)具備高信號(hào)完整性,,幫助PLL穩(wěn)定鎖相,,減少鏈路抖動(dòng)傳遞。 該系列支持可編程頻率調(diào)節(jié)(如125MHz,、156.25MHz,、200MHz),滿足以太網(wǎng),、PCIe,、Aurora等協(xié)議棧的定頻需求。頻率拉動(dòng)值支持±50~150ppm調(diào)諧,,便于與系統(tǒng)主控同步校準(zhǔn),。 FCom富士晶振VCXO采用金屬密封封裝,具有良好抗熱漂性能,,在高溫工況下依然保持±25ppm穩(wěn)定性,,適配FPGA開發(fā)板、通信主控卡及背板互連設(shè)備,。 通過將FCom的差分輸出VCXO部署于SerDes路徑,,可有效抑制串?dāng)_與時(shí)鐘歪斜,提高數(shù)據(jù)眼圖開口率與誤碼性能,,為高速接口提供可靠時(shí)鐘支撐,。差分輸出VCXO與高精度ADC完美匹配。高性能差分輸出VCXO是什么

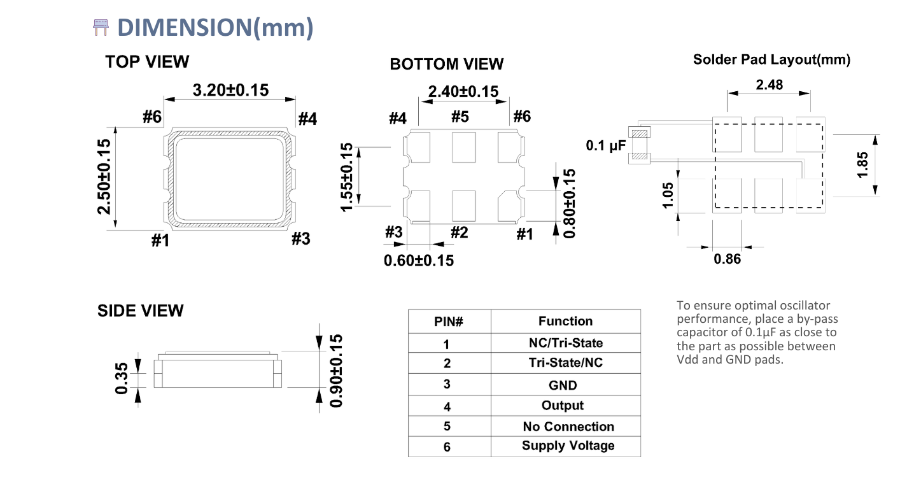

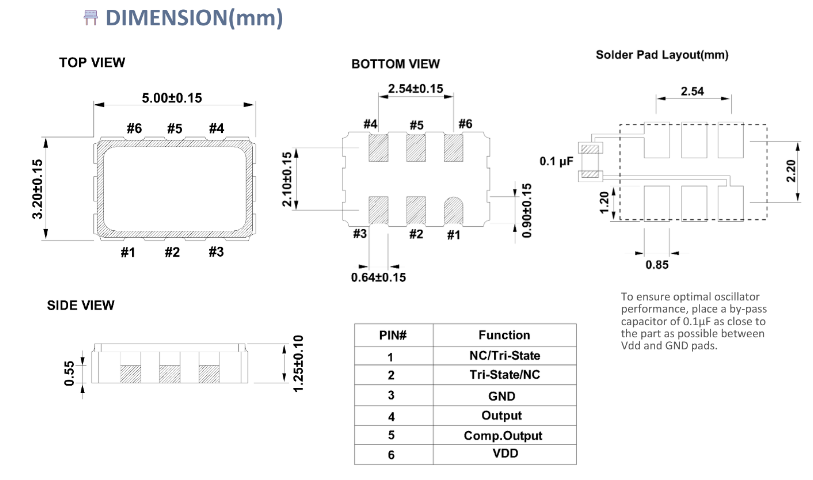

差分VCXO在SerDes高速鏈路中的同步作用 SerDes(串并轉(zhuǎn)換器)廣應(yīng)用于高速傳輸領(lǐng)域,,如以太網(wǎng),、光纖通道、PCIe、USB等,。FCom富士晶振差分輸出VCXO為其提供精確參考時(shí)鐘,,確保鏈路建立與穩(wěn)定傳輸。 SerDes鏈路如Xilinx GTY,、Intel Stratix,、TI DS125BR系列通常采用100MHz或156.25MHz的差分時(shí)鐘源,F(xiàn)Com VCXO具備0.15ps以內(nèi)的RMS抖動(dòng),,滿足眼圖和BER測試要求,。 頻率拉動(dòng)能力支持±50~100ppm,便于進(jìn)行高速鏈路訓(xùn)練期間的動(dòng)態(tài)校準(zhǔn)與多通道偏移調(diào)整,。 封裝尺寸覆蓋2520至7050,,適配不同尺寸主板與高速背板設(shè)計(jì),且封裝抗串?dāng)_結(jié)構(gòu)有助于提升信號(hào)完整性,。 差分輸出接口支持LVDS,、LVPECL或HCSL,可靈活適配各種SerDes芯片標(biāo)準(zhǔn),,為多通道同步提供標(biāo)準(zhǔn)時(shí)鐘接口,。 FCom差分輸出VCXO在SerDes系統(tǒng)中是高速通信的基礎(chǔ)構(gòu)件,突出提升系統(tǒng)鏈路質(zhì)量和互聯(lián)性能,。差分輸出VCXO怎么樣差分輸出VCXO輸出對稱,,信號(hào)更純凈。

差分VCXO在數(shù)字廣播系統(tǒng)中的時(shí)鐘支持 數(shù)字電視廣播系統(tǒng)需要多個(gè)模塊協(xié)同工作,,包括編碼,、調(diào)制、信號(hào)分發(fā)與復(fù)用,,系統(tǒng)時(shí)鐘必須具備極高一致性,。FCom富士晶振推出的差分輸出VCXO,專為數(shù)字廣播平臺(tái)提供穩(wěn)定,、精確的頻率源,。 在DVB-S2X、ATSC 3.0等標(biāo)準(zhǔn)系統(tǒng)中,,調(diào)制器,、信道編碼器與頻率合成模塊常使用VCXO作為可調(diào)諧參考,F(xiàn)Com差分VCXO能提供低抖動(dòng)信號(hào),,優(yōu)化頻道切換與多載波合成,。 VCXO具備高線性頻率調(diào)節(jié)特性,可與FPGA實(shí)現(xiàn)PLL鎖相環(huán)跟蹤,,支持常用廣播頻率如27MHz,、54MHz,、148.5MHz、297MHz等,。 該系列封裝穩(wěn)固,,EMI控制良好,具備廣播級(jí)抗溫漂能力與長期頻穩(wěn),,特別適用于衛(wèi)星發(fā)射,、地面中轉(zhuǎn)及廣播服務(wù)器平臺(tái)。 通過部署FCom富士晶振差分輸出VCXO,,數(shù)字廣播系統(tǒng)能獲得更優(yōu)的調(diào)制精度,、更低的載頻偏移,提升頻道同步與信號(hào)覆蓋質(zhì)量,。

差分VCXO在FPGA子系統(tǒng)中的多頻協(xié)同 FPGA系統(tǒng)作為靈活配置的邏輯控制平臺(tái),,其內(nèi)含的多個(gè)模塊如SerDes、高速IO,、軟核處理器等都需多個(gè)時(shí)鐘域協(xié)調(diào)工作,VCXO成為其時(shí)鐘管理系統(tǒng)的關(guān)鍵,。 FCom富士晶振差分VCXO支持13MHz~250MHz的寬頻輸出,,常見配置如25MHz、50MHz,、200MHz,,可通過LVDS、LVPECL與FPGA內(nèi)部PLL,、MMCM,、BUFG等模塊對接。 其可調(diào)特性(±50~150ppm)使得FPGA在跨時(shí)鐘域,、數(shù)據(jù)采樣或同步通信等復(fù)雜場景中能夠動(dòng)態(tài)調(diào)整參考頻率,,從而提升信號(hào)匹配率與系統(tǒng)運(yùn)行穩(wěn)定性。 FCom產(chǎn)品封裝包括7050,、5032與3225等標(biāo)準(zhǔn)尺寸,,適配Xilinx、Intel,、Lattice等多種平臺(tái),,具備高可靠性與ESD抗干擾能力。 在多通道FPGA設(shè)計(jì)中,,多個(gè)VCXO可提供不同頻率的差分時(shí)鐘,,分別用于PCIe、DDR,、Ethernet模塊等,,使整體系統(tǒng)協(xié)同運(yùn)行,,時(shí)序誤差降至低。 FCom差分VCXO通過低抖動(dòng),、高頻穩(wěn)定性特性,,為FPGA系統(tǒng)中復(fù)雜邏輯與高速接口模塊提供關(guān)鍵頻率支持,確保多頻域調(diào)度的同步與靈活性,。差分輸出VCXO的應(yīng)用貫穿從接收端到發(fā)射端,。

差分輸出VCXO在光模塊中的關(guān)鍵作用 光模塊是高速網(wǎng)絡(luò)通信系統(tǒng)的關(guān)鍵部件,其性能直接關(guān)系到數(shù)據(jù)傳輸速率與誤碼率控制,。在這類高速串行通信鏈路中,,時(shí)鐘的抖動(dòng)控制尤為關(guān)鍵。FCom富士晶振推出的差分輸出VCXO,,憑借LVPECL,、LVDS等低噪聲輸出接口,為光模塊提供了高質(zhì)量的參考時(shí)鐘,。 FCom的差分VCXO支持10MHz~250MHz頻率范圍,,輸出信號(hào)邊沿陡峭,確保在SFP/SFP+/QSFP等小型封裝光模塊中實(shí)現(xiàn)精確的時(shí)鐘調(diào)諧控制,。其差分輸出特性在抑制共模噪聲方面具備天然優(yōu)勢,,進(jìn)一步提升系統(tǒng)的信號(hào)完整性。 該系列產(chǎn)品廣支持1.8V,、2.5V,、3.3V電壓平臺(tái),并通過±50ppm頻率拉動(dòng)能力進(jìn)行動(dòng)態(tài)頻率調(diào)整,,滿足CDR(Clock Data Recovery)與SerDes的實(shí)時(shí)補(bǔ)償需求,。 FCom差分VCXO采用2520、3225等緊湊封裝形式,,結(jié)合抗振動(dòng)封裝與寬溫度設(shè)計(jì)(-40~+85℃ / -40~+125℃),,可勝任5G前傳、邊緣計(jì)算等極端部署場景,。差分輸出VCXO在電信與廣播領(lǐng)域被高度信賴,。AEC-Q200差分輸出VCXO答疑解惑

差分輸出VCXO對系統(tǒng)抖動(dòng)容限提升突出。高性能差分輸出VCXO是什么

差分VCXO在高速ADC模塊中的抖動(dòng)控制 高速模數(shù)轉(zhuǎn)換器(ADC)廣應(yīng)用于雷達(dá),、通信、醫(yī)療成像等領(lǐng)域,,其精度高度依賴于參考時(shí)鐘的穩(wěn)定性和抖動(dòng)控制。VCXO作為參考源,,尤其是具備差分輸出的低抖動(dòng)版本,,可極大提升采樣系統(tǒng)的信噪比與分辨率,。 FCom富士晶振的差分VCXO產(chǎn)品支持125MHz、250MHz,、500MHz等常用ADC參考頻率,,具備<0.15ps的低抖動(dòng)特性,,適配TI ADS54J系列,、Analog AD9208系列等前沿采樣芯片,。 差分LVDS或LVPECL接口可直接驅(qū)動(dòng)ADC的采樣時(shí)鐘輸入端,,并通過高對稱性和邊沿精確性降低采樣延遲誤差,提升系統(tǒng)的動(dòng)態(tài)性能與采樣精度,。 在需要?jiǎng)討B(tài)采樣率調(diào)整的系統(tǒng)中,,F(xiàn)Com VCXO的±100ppm拉頻能力可以實(shí)現(xiàn)靈活調(diào)諧,適應(yīng)不同帶寬、信號(hào)源或同步策略的應(yīng)用環(huán)境,。 產(chǎn)品采用金屬上蓋陶瓷封裝,,提供良好的EMI屏蔽效果和熱穩(wěn)定性,使其在多通道,、高密度ADC模塊中穩(wěn)定運(yùn)行,,避免時(shí)鐘污染與串?dāng)_。 FCom差分VCXO為ADC采樣提供精確低噪聲時(shí)鐘支撐,,是提升信號(hào)處理系統(tǒng)性能的關(guān)鍵組件,,尤其適用于高頻,、高速和高精度測量場景。高性能差分輸出VCXO是什么

- FVC-3L-PG差分輸出VCXO誠信合作 2025-06-22

- 通信設(shè)備高精度振蕩器選型實(shí)戰(zhàn)指南 2025-06-22

- Zigbee/LoRa模塊32.768kHz振蕩器適配NXP/ADI RTC芯片 2025-06-22

- 優(yōu)勢差分輸出VCXO技術(shù)指導(dǎo) 2025-06-22

- 網(wǎng)絡(luò)設(shè)備低功耗振蕩器選型實(shí)戰(zhàn)指南 2025-06-22

- 量子計(jì)算低抖動(dòng)差分振蕩器 2025-06-22

- 高性能差分輸出VCXO廠家供應(yīng) 2025-06-22

- FCO2CUP低功耗振蕩器EMI性能的影響 2025-06-22

- FCO-3C-LE低EMI振蕩器批發(fā)有優(yōu)惠嗎 2025-06-22

- FVC5LPG差分輸出VCXO客服電話 2025-06-21

- 天津國產(chǎn)FPGA開發(fā)板教學(xué) 2025-06-22

- 蘇州質(zhì)量充電樁銷售銷售 2025-06-22

- 陜西中活性助焊劑廠家精選 2025-06-22

- 高清LED戶外菱形屏價(jià)錢 2025-06-22

- 深圳3C數(shù)碼芯片方案設(shè)計(jì)開發(fā)費(fèi)用 2025-06-22

- 青海高科技AH401F 2025-06-22

- 安徽耐用電源管理芯片公司 2025-06-22

- 吉林智能LDO芯片型號(hào) 2025-06-22

- 虎丘區(qū)智能IGBT模塊報(bào)價(jià) 2025-06-22

- 宜興通用電子元器件銷售廠家供應(yīng) 2025-06-22