南京UFS分析儀品牌

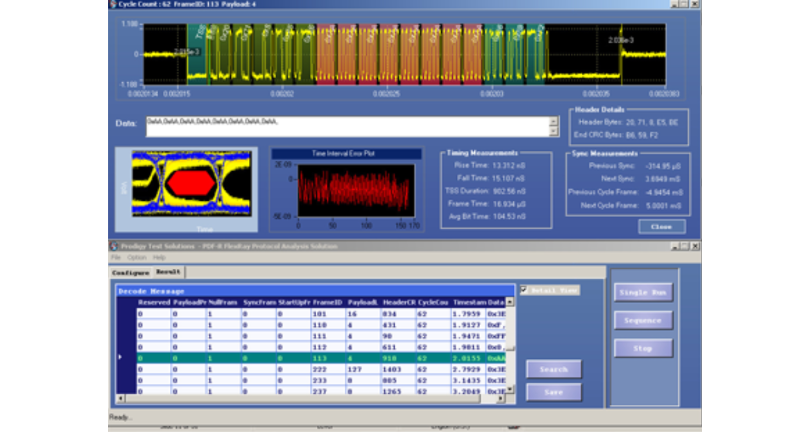

在跳變定時中,,每個序列步驟只有2個分支。在跳變時序中,,只有一個全局計數器可用,。跳變時序需要有時間標簽才能重建數據。通過將時間標簽與內存中的測量數據交叉可存儲時間標簽,。默認情況下,,分析儀將查找為邏輯分析儀模塊定義的所有總線/信號上的轉變。但是,,為增加可用內存深度和采集時間,,可以在高級觸發(fā)中選擇不存儲某些總線/信號轉變(如將無用信息添加到測量中的時鐘或選沖信號)。運行測量時,,無論總線/信號是否定義或是否分配給邏輯分析儀通道,,都將在所有這些通道上采集數據。在跳變時序模式中,,如果定義的總線/信號(未排除的)上存在轉變,,將保存采集的樣本。運行跳變時序測量后,。如果為以前未分配的邏輯分析儀通道定義新的總線/信號,,那么將顯示在這些通道上采集的數據,但是不可能存儲這些總線/信號上的所有轉變,;顯示的數據好似新的總線/信號在運行測量前就已經被排除了,。在跳變時序中,不需要預先存儲數據(觸發(fā)前獲得的樣本),。因此,,與狀態(tài)模式非常相似的是,觸發(fā)位置(起始/中心/結束)表明觸發(fā)后樣本占用內存的百分比,。歐奧電子是Prodigy在中國區(qū)的官方授權合作伙伴,,ProdigyMPHY,UniPro,UFS總線協(xié)議分析儀測試解決方案不會收到EAR進出口方面的管制。I2S協(xié)議分析儀/訓練器找歐奧,!南京UFS分析儀品牌

才能符合此表達式,。換句話說,在ADDR等于1000的同時DATA等于2000,。因此,,如果要在同時發(fā)生兩個事件時觸發(fā),則應使用布爾邏輯表達式,。常見錯誤是應使用布爾邏輯表達式時嘗試使用兩個序列步驟,,或者應使用兩個序列步驟時嘗試使用布爾邏輯表達式。當多個事件同時發(fā)生時使用布爾邏輯表達式,,而在一個事件接著一個事件發(fā)生時使用多個序列步驟,。分支:分支類似于C編程語言中的Switch語句和Basic中的SelectCase語句。分支可提供測試多個sADDR”。多數邏輯分析儀還支持“notinrange”功能,。范圍是一種方便的快捷方式,,因此您無需指定“ADDR>=1000andADDR<=>標志:標志是用于從一個模塊向另一個模塊發(fā)送信號的布爾變量。當某種情況在某一模塊中發(fā)生而稍后被另一模塊測試時可以設置標志,。在下面的示例中,,標志1用于跟蹤在模塊1的觸發(fā)序列中發(fā)生的情況,如,,如果想在ADDR=1000第5次出現時觸發(fā),,可以將觸發(fā)設置為:IfADDR=1000occurs5timesthenTrigger全局計數器類似于整數變量。全局計數器比發(fā)生計數器更靈活,,因為它們可用于為復雜事件(例如一個時鐘沿后跟另一時鐘沿的事件)計數,。可以增加,、測試和重新設置全局計數器,。默認情況下,全局計數器以零開頭并且不需要重新設置,。梅州I3C分析儀費用100BaseTl (Automotive)協(xié)議分析儀/訓練器找歐奧,!

定時分析儀對輸入通道進行采樣時,該通道信號或者是高電平或者是低電平,。歐奧電子是Prodigy在中國區(qū)的官方授權合作伙伴,,ProdigyMPHY,UniPro,UFS總線協(xié)議分析儀測試解決方案不會收到EAR進出口方面的管制。同時還有代理其他總類的協(xié)議分析儀,,包括嵌入式設備用的SDIO協(xié)議分析儀,QSPI協(xié)議分析儀及訓練器,I3C協(xié)議分析儀及訓練器,RFFE協(xié)議分析儀及訓練器等等,。我司還有代理SPMI協(xié)議分析儀及訓練器,車載以太網分析儀,以及各種相關的基于示波器的解碼軟件和SI測試軟件,。同時,歐奧電子也有提供高難度焊接,,以及高速信號,,如UFS,DDR3/DDR4,,USBtypeC等高速協(xié)議抓取和分析的服務,。如果在進行某一采樣時該通道處于某種狀態(tài)(高或低),而在進行下一采樣時變成了相反的狀態(tài),。則分析儀可以“知道”輸入信號已在這兩個采樣之間的某個時候發(fā)生了跳變,。但它不知道具體在何時,因此它將跳變點放在了后一個采樣上,,如下圖所示,。圖3定時分析采樣精度(不確定度)對于跳變實際上是在何時發(fā)生以及分析儀何時顯示跳變,存在著某種含糊性。假如跳變是在前一個采樣點之后立即發(fā)生的,,這種不確定性多也就是一個采樣周期,。不過對于這種方法,在精度和總采樣時間之間也存在著一種折衷,。請記住,。

邏輯分析的概念邏輯分析儀也是非常常用的儀表,與示波器一樣,,是數字設計和測量的經典儀器之一,。數字電路測量時,何時應使用示波器呢,?一般而言,,當需要精確參數信息(如時間間隔和電壓讀數)時可以使用示波器。具體來講:當需要測量信號的較小電壓偏移(如低于或超出)時,。當需要較高的時間間隔精度時,。示波器能夠采集精確的參數信息,如脈沖的上升沿上兩點之間的高精度時間,。圖1示波器用于測量信號的模擬波形一般而言,,邏輯分析儀用于查看多個信號之間的定時關系,或者用于捕獲信號所運載的數據,。當被測設備的信號超過電壓閥值時,,邏輯分析儀會表現出與邏輯電路相同的反應。它將識別信號的高低,。具體來講:當需要立即查看多個信號時,。邏輯分析儀可以很好地組織和顯示多個信號。一般任務是將多個信號組成一條總線并分配一個自定義名稱,。地址,、數據和控制總線都是有性的示例。當需要使用與硬件相同的方式查看系統(tǒng)中的信號時,。信號顯示在一個時間軸上,,這樣就可以查看相對于其他總線信號或時鐘信號的轉變的發(fā)生時間。當需要象接收芯片一樣基于時鐘邊沿,,捕獲總線中的信息時,。接收芯片基于時鐘邊沿判斷總線上的地址、命令和數據,。邏輯分析儀象一個偵聽器,。I3C訓練器協(xié)議分析儀/訓練器找歐奧!

內存深度設置為總采集內存的1/2,。所有盒對都可用于采集數據,。如果選擇整個內存,則要用于時間標簽存儲的默認Pod是左邊的盒對,但未分配總線或信號的任何Pod都是可以使用的,。跳變定時模式,,時間標簽存儲需要1個Pod或1/2的采集內存:跳變時序采樣模式也需要時間標簽存儲。當選擇小采樣周期時,,必須將一個Pod對保留用于時間標簽存儲,。在這種情況下,不能使用1/2(或更少)的模塊采集內存來替代該Pod,。對于其他采樣周期,,內存深度和通道數的權衡與狀態(tài)采樣模式下的相同。也就是說,,要使用1/2以上的模塊采集內存,,必須將一個Pod保留用于時間標簽存儲。要使用所有Pod,,內存使用量不能超過模塊采集內存的1/2,。一般來說,可用定時器數與那些不屬于為時間標簽存儲而保留的Pod數相同,。狀態(tài)模式采樣位置,、眼定位和眼圖掃描同步采樣(狀態(tài)模式)邏輯分析儀與觸發(fā)時鐘沿的觸發(fā)相似,因為它們都需要輸入邏輯信號才可以在時鐘事件前(建立時間)和時鐘事件后(保持時間)的一段時間內保持穩(wěn)定,,以便正確解釋邏輯電平,。組合建立和保持時間被稱為建立/保持窗口。被測設備(由于其本身的建立/保持要求)可指定數據在某段時間內在總線上有效,。這被稱為數據有效窗口,。一般情況下。分析儀哪家強,?歐奧強,!汕尾SD分析儀報價

訓練器廠家哪家好?歐奧電子好,!南京UFS分析儀品牌

同時,,歐奧電子也有提供高難度焊接,以及高速信號,,如UFS,,DDR3/DDR4,,USBtypeC等高速協(xié)議抓取和分析的服務,。即使度個樣本符合觸發(fā)條件,邏輯分析儀也只觸發(fā)一次,。例如,,使用的問題是“如果不符合序列步驟中的條件會怎樣?”例如,有一個條件是“IfADDR=1000ThenTrigger”,,那么如果當前樣本是ADDR=2000,,結果會怎樣?邏輯分析儀只采集下一樣本并試圖再次執(zhí)行此序列步驟,。實際上,,如果觸發(fā)條件是“ADDR=1000”,這相當于“持續(xù)采集樣本直到找到條件為ADDR=1000的樣本”,。因此,,如果設置一個從不符合的觸發(fā)條件,邏輯分析器將不會觸發(fā),。當符合序列步驟中的條件時,,使用“轉到”操作時下一步將執(zhí)行哪個序列步驟將會非常清楚,但是如果沒有使用“轉到”操作,。則不可能知道執(zhí)行哪個序列步驟,。在一些邏輯分析儀上,如果沒有“轉到”,,這意味著應當執(zhí)行下一序列步驟,。在其他邏輯分析儀上,意味著將再次執(zhí)行同一序列步驟,。由于比較混亂,,好使用“轉到”操作而不依靠默認。狀態(tài)和定時模塊通過在每個序列步驟中自動包含一個“轉到”或“觸發(fā)”操作來解決這一問題,。例如:IfADDR=1000andDATA=2000thenGoto1布爾邏輯表達式:當多個序列步驟表示“后跟”時,。南京UFS分析儀品牌

- 汕尾SDIO分析儀收費 2025-06-25

- 寧波UART分析儀費用 2025-06-25

- 肇慶EMMC分析儀報價 2025-06-25

- 福州協(xié)議分析儀電話 2025-06-25

- 蘇州分析儀費用 2025-06-25

- 北京SD協(xié)議分析儀收費 2025-06-25

- 中山USB分析儀廠家 2025-06-25

- 長沙SD分析儀費用 2025-06-25

- 深圳USB分析儀售價 2025-06-25

- 福州RFFE分析儀售價 2025-06-25

- 南京華璧氣相色譜儀廠家 2025-06-25

- 政企客戶專線光纜監(jiān)測廠家聯系電話 2025-06-25

- 手提礦物礦渣含量光譜儀分析儀器 2025-06-25

- 手提鋁合金金屬元素光譜儀 2025-06-25

- 崇明區(qū)質量儀器儀表選擇 2025-06-25

- 溫州SS304止回閥定制 2025-06-25

- 江蘇塵埃粒子計數器計量校準 2025-06-25

- 江蘇智能液相色譜哪家便宜 2025-06-25

- 黑龍江真空蝶閥工作原理 2025-06-25

- 深圳本地光學儀器推薦廠家 2025-06-25