安徽儲能設(shè)備硬件開發(fā)流程

FPGA(Field-ProgrammableGateArray,,現(xiàn)場可編程門陣列)硬件設(shè)計(jì)雖然具有諸多優(yōu)勢,,如高靈活性,、高性能,、低功耗等,但也存在一些缺點(diǎn),。1.成本高設(shè)計(jì)成本:FPGA芯片的設(shè)計(jì)和開發(fā)需要較高的技術(shù)投入和復(fù)雜的工程流程,,包括硬件描述語言(HDL)編程、仿真,、綜合,、布局布線等多個(gè)步驟,這些都需要專業(yè)的工程師和昂貴的開發(fā)工具,。2.硬件資源有限邏輯資源限制:FPGA芯片內(nèi)部包含一定數(shù)量的邏輯塊,、IO接口、存儲資源等,,這些資源是有限的,。在設(shè)計(jì)復(fù)雜的系統(tǒng)時(shí),可能會遇到資源不足的問題,,需要優(yōu)化設(shè)計(jì)或選擇更高性能的FPGA芯片.3.時(shí)序設(shè)計(jì)復(fù)雜時(shí)鐘管理:FPGA的時(shí)鐘管理相對復(fù)雜,,需要仔細(xì)設(shè)計(jì)和設(shè)置時(shí)鐘域、時(shí)鐘同步,、時(shí)鐘分頻等,。4.開發(fā)周期長設(shè)計(jì)驗(yàn)證:FPGA設(shè)計(jì)需要經(jīng)過多個(gè)階段的驗(yàn)證,包括功能驗(yàn)證,、時(shí)序驗(yàn)證,、物理驗(yàn)證等。5.技術(shù)門檻高專業(yè)知識要求:FPGA設(shè)計(jì)需要掌握硬件描述語言,、數(shù)字電路設(shè)計(jì),、計(jì)算機(jī)架構(gòu)等多方面的知識。這些知識的獲取和掌握需要較長的時(shí)間和努力,。人才短缺:由于FPGA技術(shù)的專業(yè)性和復(fù)雜性,,相關(guān)人才相對短缺。這可能導(dǎo)致項(xiàng)目在招聘和團(tuán)隊(duì)建設(shè)方面遇到困難,。 學(xué)習(xí)硬件設(shè)計(jì)需要長期堅(jiān)持不懈的知識儲備和積累,,在實(shí)際應(yīng)用中積累硬件設(shè)計(jì)的經(jīng)驗(yàn)。安徽儲能設(shè)備硬件開發(fā)流程

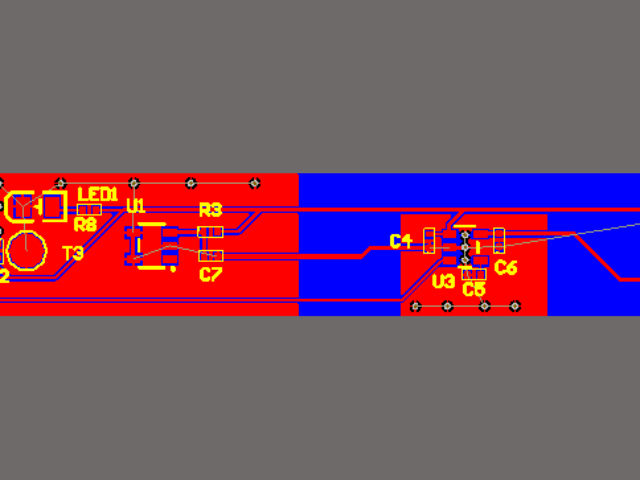

硬件開發(fā)

物聯(lián)網(wǎng)硬件開發(fā)的未來趨勢與挑戰(zhàn)一,、未來趨勢邊緣計(jì)算的普及,,邊緣計(jì)算通過將數(shù)據(jù)處理和分析任務(wù)轉(zhuǎn)移到設(shè)備邊緣,降低了網(wǎng)絡(luò)帶寬需求和延遲,,提高了數(shù)據(jù)處理效率和安全性,。二、面臨的挑戰(zhàn)數(shù)據(jù)安全與隱私保護(hù):隨著物聯(lián)網(wǎng)設(shè)備的普及和應(yīng)用場景的拓展,,數(shù)據(jù)安全與隱私保護(hù)問題日益凸顯,。三、改進(jìn)方向加強(qiáng)技術(shù)研發(fā)與創(chuàng)新:不斷投入研發(fā)資源,,加強(qiáng)技術(shù)創(chuàng)新和突破,,推動物聯(lián)網(wǎng)硬件技術(shù)的持續(xù)發(fā)展。同時(shí),,積極引進(jìn)和消化技術(shù)成果,,提升我國物聯(lián)網(wǎng)硬件的核心競爭力。完善標(biāo)準(zhǔn)體系與互操作性:推動物聯(lián)網(wǎng)標(biāo)準(zhǔn)的制定和完善工作,,建立統(tǒng)一的標(biāo)準(zhǔn)體系和技術(shù)規(guī)范,。加強(qiáng)不同設(shè)備之間的互操作性測試和驗(yàn)證工作,確保不同設(shè)備之間的無縫連接和協(xié)同工作,。強(qiáng)化數(shù)據(jù)安全與隱私保護(hù):加強(qiáng)物聯(lián)網(wǎng)設(shè)備的數(shù)據(jù)安全設(shè)計(jì)和保護(hù)措施,,采用加密技術(shù)和安全協(xié)議確保數(shù)據(jù)傳輸和存儲的安全性。同時(shí),,建立完善的隱私保護(hù)機(jī)制和政策法規(guī)體系,,保障用戶的隱私權(quán)益不受侵犯。降低技術(shù)復(fù)雜性與成本:通過優(yōu)化設(shè)計(jì)方案,、提高生產(chǎn)效率等方式降低物聯(lián)網(wǎng)硬件的技術(shù)復(fù)雜性和成本,。同時(shí),,積極推廣和應(yīng)用成熟的技術(shù)和產(chǎn)品方案,降低用戶的經(jīng)濟(jì)負(fù)擔(dān)和使用門檻,。 山東光伏硬件開發(fā)交期不懂元器件的基本原理,,參數(shù)選型,是無法正常開展硬件開發(fā)工作的,。

硬件設(shè)計(jì)的復(fù)雜性標(biāo)題:硬件開發(fā)的復(fù)雜性挑戰(zhàn)在硬件開發(fā)的領(lǐng)域,,設(shè)計(jì)的復(fù)雜性是開發(fā)者經(jīng)常面臨的一大難點(diǎn)。隨著技術(shù)的不斷進(jìn)步,,現(xiàn)代硬件設(shè)備往往集成了大量的功能模塊,,包括處理器、內(nèi)存,、存儲設(shè)備,、通信接口以及各類傳感器等。這些模塊之間的互操作性,、信號完整性,、功耗管理以及電磁兼容性等問題,都需要開發(fā)者在設(shè)計(jì)階段就進(jìn)行周密的考慮和規(guī)劃,。首先,,模塊之間的互操作性要求開發(fā)者對各個(gè)模塊的技術(shù)規(guī)格有深入的理解,以確保它們,。能夠無縫地協(xié)同工作這涉及到大量的接口協(xié)議,、時(shí)序要求以及數(shù)據(jù)傳輸速率的匹配等問題。其次,,信號完整性問題也是硬件設(shè)計(jì)中的一個(gè)重要挑戰(zhàn),。高速信號在傳輸過程中容易受到干擾和衰減,導(dǎo)致信號質(zhì)量下降甚至丟失,。因此,,開發(fā)者需要采用先進(jìn)的信號完整性仿真工具和方法,對設(shè)計(jì)進(jìn)行精確的分析和優(yōu)化,。此外,,功耗管理也是硬件設(shè)計(jì)中的一個(gè)重要方面。隨著能源問題的日益突出,,如何在保證設(shè)備性能的同時(shí)降低功耗,,成為了開發(fā)者必須面對的問題。這要求開發(fā)者在電路設(shè)計(jì)和軟件算法上進(jìn)行創(chuàng)新,,以實(shí)現(xiàn)高效的能源利用,。

多功能數(shù)據(jù)采集器硬件設(shè)計(jì)技巧——高精度數(shù)據(jù)采集與轉(zhuǎn)換數(shù)據(jù)采集的精度和轉(zhuǎn)換效率直接影響到多功能數(shù)據(jù)采集器的性能。在硬件設(shè)計(jì)中,A/D轉(zhuǎn)換電路是實(shí)現(xiàn)高精度數(shù)據(jù)采集的關(guān)鍵部分,。選擇合適的ADC(模數(shù)轉(zhuǎn)換器)芯片,,并合理設(shè)計(jì)其外圍電路,對于提高數(shù)據(jù)采集精度和轉(zhuǎn)換效率具有重要意義,。設(shè)計(jì)技巧:ADC選型:根據(jù)數(shù)據(jù)采集器的精度要求,,選擇具有高分辨率、低噪聲,、低漂移等特性的ADC芯片。同時(shí),,考慮其采樣率和功耗等參數(shù),,確保滿足設(shè)計(jì)要求。參考電壓設(shè)計(jì):穩(wěn)定的參考電壓是ADC正常工作的基礎(chǔ),。在設(shè)計(jì)中,,應(yīng)選用高精度的參考電壓源,并合理設(shè)計(jì)其濾波和去耦電路,,以減少噪聲和干擾,。信號調(diào)理:在ADC之前,對輸入信號進(jìn)行適當(dāng)?shù)恼{(diào)理和濾波,,以去除噪聲和干擾信號,,提高數(shù)據(jù)采集的精度和穩(wěn)定性。同時(shí),,考慮信號的放大和衰減等處理,,以適應(yīng)不同量程的輸入信號。 硬件開發(fā)面臨著諸多挑戰(zhàn),,如性能和功耗的平衡,、硬件和軟件的協(xié)同設(shè)計(jì)、安全性等,。

硬件設(shè)計(jì)的可擴(kuò)展性包含多個(gè)方面,,這些方面共同構(gòu)成了硬件系統(tǒng)在面對性能需求增長時(shí)能夠靈活調(diào)整、擴(kuò)展和升級的能力,。以下是硬件設(shè)計(jì)可擴(kuò)展性的一些主要方面:模塊化設(shè)計(jì):模塊化設(shè)計(jì)是硬件可擴(kuò)展性的基礎(chǔ),。通過將硬件系統(tǒng)劃分為多個(gè)功能完整的模塊,可以方便地增加,、替換或升級某個(gè)模塊,,而不需要對整個(gè)系統(tǒng)進(jìn)行大規(guī)模改動。這種設(shè)計(jì)方式提高了系統(tǒng)的靈活性和可維護(hù)性,。標(biāo)準(zhǔn)化接口:采用標(biāo)準(zhǔn)化的接口和協(xié)議可以確保不同模塊之間的兼容性和互換性,。當(dāng)需要擴(kuò)展系統(tǒng)時(shí),只需選擇符合標(biāo)準(zhǔn)的模塊進(jìn)行接入,即可實(shí)現(xiàn)系統(tǒng)的擴(kuò)展和升級,??蓴U(kuò)展的硬件資源:硬件設(shè)計(jì)應(yīng)預(yù)留足夠的資源空間,以便在未來需要時(shí)能夠輕松地增加計(jì)算節(jié)點(diǎn),、內(nèi)存,、存儲等硬件資源。綜上所述,,硬件設(shè)計(jì)的可擴(kuò)展性是一個(gè)綜合性的概念,,涉及到模塊化設(shè)計(jì)、標(biāo)準(zhǔn)化接口,、可擴(kuò)展的硬件資源,、靈活的架構(gòu)設(shè)計(jì)、易于升級和維護(hù),、兼容性考慮以及可擴(kuò)展的通信能力等多個(gè)方面,。通過優(yōu)化這些方面的設(shè)計(jì),可以構(gòu)建出具有高可擴(kuò)展性的硬件系統(tǒng),,以應(yīng)對未來不斷增長的性能需求,。 好的硬件工程師就是一個(gè)項(xiàng)目經(jīng)理,他需要從外界獲取對自己設(shè)計(jì)的需求,,然后匯總,,分析成具體的硬件實(shí)現(xiàn)。分析儀器設(shè)備硬件開發(fā)功能

現(xiàn)在的硬件設(shè)計(jì)更趨向國產(chǎn)化替代,?安徽儲能設(shè)備硬件開發(fā)流程

硬件供應(yīng)鏈與降低成本的挑戰(zhàn)標(biāo)題:硬件供應(yīng)鏈與降低成本的困境在硬件開發(fā)過程中,,供應(yīng)鏈管理和降低成本是另外兩個(gè)重要的難點(diǎn)。隨著全球化的發(fā)展,,硬件供應(yīng)鏈變得越來越復(fù)雜和不可預(yù)測,,這給開發(fā)者帶來了巨大的挑戰(zhàn)。首先,,硬件供應(yīng)鏈的可靠性是一個(gè)關(guān)鍵問題,。由于硬件系統(tǒng)包含多個(gè)組件和模塊,這些組件和模塊往往來自不同的供應(yīng)商和地區(qū),。因此,,開發(fā)者需要建立穩(wěn)定的供應(yīng)鏈關(guān)系,確保組件和模塊的供應(yīng)及時(shí),、可靠,。然而,在實(shí)際操作中,,由于各種不可預(yù)見因素的影響,,供應(yīng)鏈的可靠性往往難以保證。其次,硬件降低成本也是一個(gè)難題,。隨著技術(shù)的不斷進(jìn)步和市場競爭的加劇,,硬件成本不斷下降。然而,,在保證產(chǎn)品性能和質(zhì)量的前提下降低成本并非易事,。開發(fā)者需要在設(shè)計(jì)階段就進(jìn)行成本優(yōu)化和降低成本,同時(shí)還需要在供應(yīng)鏈管理中與供應(yīng)商進(jìn)行深入的談判和合作,。此外,,硬件開發(fā)的周期性和更新?lián)Q代也給降低成本帶來了挑戰(zhàn)。由于技術(shù)更新迅速,,硬件產(chǎn)品往往需要在短時(shí)間內(nèi)完成從設(shè)計(jì)到量產(chǎn)的全過程,。這要求開發(fā)者在有限的時(shí)間內(nèi)完成大量的工作,并在保證質(zhì)量的前提下降低成本,。因此,如何平衡時(shí)間,、質(zhì)量和成本之間的關(guān)系,,成為了硬件開發(fā)者必須面對的問題。 安徽儲能設(shè)備硬件開發(fā)流程

南京億芯智研儀器設(shè)備有限公司匯集了大量的優(yōu)秀人才,,集企業(yè)奇思,,創(chuàng)經(jīng)濟(jì)奇跡,一群有夢想有朝氣的團(tuán)隊(duì)不斷在前進(jìn)的道路上開創(chuàng)新天地,,繪畫新藍(lán)圖,,在江蘇省等地區(qū)的儀器儀表中始終保持良好的信譽(yù),信奉著“爭取每一個(gè)客戶不容易,,失去每一個(gè)用戶很簡單”的理念,,市場是企業(yè)的方向,質(zhì)量是企業(yè)的生命,,在公司有效方針的領(lǐng)導(dǎo)下,,全體上下,團(tuán)結(jié)一致,,共同進(jìn)退,,**協(xié)力把各方面工作做得更好,努力開創(chuàng)工作的新局面,,公司的新高度,,未來南京億芯智研儀器設(shè)備供應(yīng)和您一起奔向更美好的未來,即使現(xiàn)在有一點(diǎn)小小的成績,,也不足以驕傲,,過去的種種都已成為昨日我們只有總結(jié)經(jīng)驗(yàn),才能繼續(xù)上路,讓我們一起點(diǎn)燃新的希望,,放飛新的夢想,!

- 江蘇分析儀器設(shè)備硬件開發(fā)需求 2024-12-19

- 福建風(fēng)力發(fā)電硬件開發(fā)注意事項(xiàng) 2024-12-19

- 山東檢測儀器設(shè)備硬件開發(fā)測試 2024-12-19

- 北京汽車新能源硬件開發(fā)環(huán)境 2024-12-18

- 江西電子科技產(chǎn)品硬件開發(fā)環(huán)境 2024-12-18

- 江西電子科技產(chǎn)品硬件開發(fā)管理規(guī)范 2024-12-18

- 浙江儲能設(shè)備硬件開發(fā)測試 2024-12-17

- 數(shù)據(jù)采集器硬件開發(fā)應(yīng)用 2024-12-17

- 江西硬件開發(fā)費(fèi)用 2024-12-17

- 內(nèi)蒙古檢測儀器設(shè)備硬件開發(fā)分類 2024-12-16

- 河南豚鼠模式動物儀器廠家 2025-06-23

- 嘉興一鍵閃測影像儀多少錢 2025-06-23

- 衢州海克斯康影像儀圖片 2025-06-23

- 廣西本地多維力傳感器檢修 2025-06-23

- 奧林巴斯XRF合金快速元素分析光譜儀 2025-06-23

- 玉田導(dǎo)熱油液位計(jì)生產(chǎn)企業(yè) 2025-06-23

- 寧波電子影像儀直銷價(jià)格 2025-06-23

- 重慶流量儀表選型 2025-06-23

- 安徽專業(yè)防爆冰箱溫度范圍 2025-06-23

- 江蘇耐高溫多維力傳感器廠家報(bào)價(jià) 2025-06-23