內(nèi)蒙古光伏硬件開發(fā)調(diào)試

物聯(lián)網(wǎng)硬件開發(fā)的創(chuàng)新與應用:隨著傳感器技術,、低功耗芯片和無線通信技術的不斷進步,,可穿戴設備在功能,、續(xù)航和用戶體驗上實現(xiàn)提升,。例如,,智能手環(huán)、智能手表等設備不僅能夠監(jiān)測心率,、血壓等生理指標,,還能實現(xiàn)運動追蹤、消息提醒等功能,。應用拓展:運動健身,、智能家居等領域展現(xiàn)出廣泛的應用前景。用戶可以通過智能手機或智能音箱等設備對家居環(huán)境進行實時監(jiān)控和調(diào)節(jié),,提高生活便捷性和舒適度,。物聯(lián)網(wǎng)硬件開發(fā)的創(chuàng)新方法改進硬件開發(fā)流程模塊化設計:采用模塊化設計思想將硬件系統(tǒng)劃分為多個模塊進行開發(fā),降低開發(fā)難度和成本,。同時,,模塊化設計還便于系統(tǒng)的升級和維護。四,、物聯(lián)網(wǎng)硬件應用的未來發(fā)展方向智能化:隨著人工智能技術的不斷發(fā)展,,物聯(lián)網(wǎng)硬件設備將更加智能化。通過集成AI算法和模型,,物聯(lián)網(wǎng)設備將具備更強的自學習和自適應能力,,能夠根據(jù)用戶行為和環(huán)境變化自動調(diào)整和優(yōu)化性能。硬件不會像軟件一樣代碼錯了修改一下幾分鐘就搞定,,硬件設計錯了,,那可能要重來,整個周期就要延遲,。內(nèi)蒙古光伏硬件開發(fā)調(diào)試

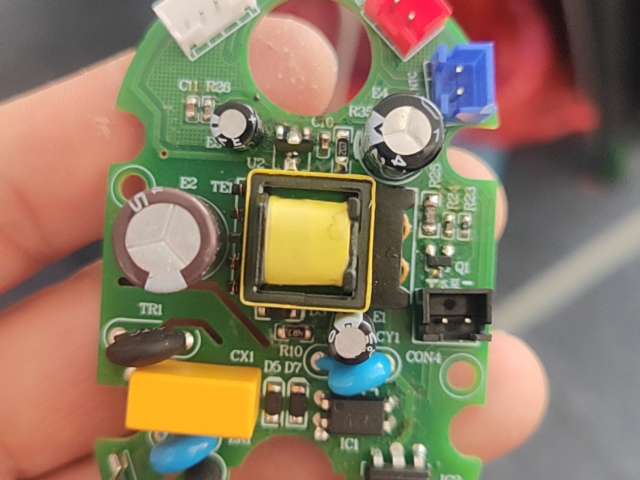

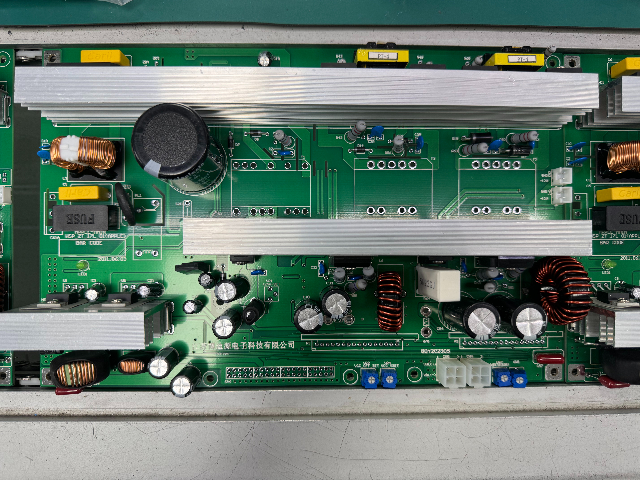

硬件開發(fā)

設計PCB時使用蛇形走線(也被稱為蛇行,、蜿蜒或曲折布線)是出于多種考慮,主要包括以下幾個方面:一,、信號完整性減少信號反射和串擾:在高速電子設備中,,信號完整性至關重要。蛇形走線通過增加信號線的物理長度和改變其形狀,,有助于減少信號的反射和串擾,,二、時延匹配同步信號:對于差分信號或同步信號,,時延匹配至關重要,。蛇形走線可以更容易地實現(xiàn)時延匹配,確保信號同時到達目的地,,從而維持系統(tǒng)的時序準確性,。三、電磁兼容性(EMC)減少電磁干擾(EMI):蛇形走線可以減少回流路徑的長度,,降低電流回流時產(chǎn)生的電磁場,,從而減少輻射和敏感信號的干擾,。四、空間利用和布局優(yōu)化填充空白區(qū)域:PCB布局中常常存在一些不規(guī)則的空白區(qū)域,,無法容納直線走線,。五、特殊應用代替保險絲提供過載保護:蛇形走線通過特定的設計可以限制通過它的電流,,從而起到類似保險絲的保護作用,。但這種方法可靠性可能較低,需謹慎使用,。 內(nèi)蒙古數(shù)據(jù)采集器硬件開發(fā)測試硬件開發(fā)的發(fā)展趨勢是多元化的,涉及技術,、設計,、生產(chǎn)等多個層面。

多功能數(shù)據(jù)采集器硬件設計技巧——通信與隔離技術在多功能數(shù)據(jù)采集器的硬件設計中,,通信與隔離技術也是不可忽視的重要環(huán)節(jié),。通信電路的設計應確保數(shù)據(jù)采集器與上位機或其他設備之間的數(shù)據(jù)傳輸穩(wěn)定可靠;而隔離技術的應用則可以降低電路間的干擾和噪聲,,提高系統(tǒng)的整體性能,。設計技巧:通信電路設計:根據(jù)實際需求選擇合適的通信協(xié)議和接口,如RS-232,、RS-485,、CAN總線等。在設計中,,應確保通信電路的抗干擾能力強,、傳輸速度快、通信距離遠,。同時,,考慮通信數(shù)據(jù)的校驗和糾錯機制,以提高數(shù)據(jù)傳輸?shù)目煽啃?。隔離技術應用:在數(shù)據(jù)采集器的設計中,,采用隔離技術可以降低電路間的干擾和噪聲。例如,,在指令信號的傳輸中,,可以使用數(shù)字隔離芯片進行隔離處理;在模擬信號的傳輸中,,可以采用變壓器或光耦等隔離器件進行隔離,。這些措施可以降低環(huán)路噪聲和共模干擾的影響,提高系統(tǒng)的穩(wěn)定性和可靠性,。接口擴展與兼容性:在設計中,,應充分考慮數(shù)據(jù)采集器的接口擴展性和兼容性,。通過預留足夠的接口資源和采用標準的接口協(xié)議,可以方便地與其他設備進行連接和通信,。同時,,考慮不同型號和品牌的設備之間的兼容性問題,以確保數(shù)據(jù)采集器能夠廣泛應用于各種場合,。

硬件開發(fā)的難點主要體現(xiàn)在多個方面,,這些難點不僅考驗著開發(fā)者的技能,還涉及到項目管理,、團隊協(xié)作,、技術創(chuàng)新等多個層面。以下是一些主要的難點:1.設計與實現(xiàn)復雜性高:硬件產(chǎn)品的設計需要考慮眾多因素,,如功能需求,、性能指標、降低成本,、可制造性等,,這些都需要開發(fā)者具備深厚的知識和豐富的實踐經(jīng)驗。2.供應鏈管理多供應商協(xié)調(diào):硬件產(chǎn)品的生產(chǎn)往往涉及多個供應商和制造商,,如何管理供應鏈,,確保原材料和零部件的質(zhì)量、交期和成本,,是開發(fā)者需要面對的重要問題,。3.質(zhì)量制定標準:硬件產(chǎn)品的質(zhì)量直接關系到用戶的使用體驗和企業(yè)的聲譽,因此,,開發(fā)者需要制定嚴格的質(zhì)量標準和測試流程,,確保產(chǎn)品的各項指標符合要求。4.降低成本成本構成復雜:硬件產(chǎn)品的成本包括原材料成本,、制造成本,、研發(fā)成本等多個方面,如何在保證產(chǎn)品質(zhì)量的同時,,合理降低成本成本,,是開發(fā)者需要權衡的問題。 在公司的規(guī)范化管理中,,硬件開發(fā)的規(guī)范化是一項重要內(nèi)容,。

多功能數(shù)據(jù)采集器硬件設計技巧——高精度數(shù)據(jù)采集與轉換數(shù)據(jù)采集的精度和轉換效率直接影響到多功能數(shù)據(jù)采集器的性能。在硬件設計中,,A/D轉換電路是實現(xiàn)高精度數(shù)據(jù)采集的關鍵部分,。選擇合適的ADC(模數(shù)轉換器)芯片,并合理設計其外圍電路,,對于提高數(shù)據(jù)采集精度和轉換效率具有重要意義,。設計技巧:ADC選型:根據(jù)數(shù)據(jù)采集器的精度要求,,選擇具有高分辨率、低噪聲,、低漂移等特性的ADC芯片,。同時,考慮其采樣率和功耗等參數(shù),,確保滿足設計要求,。參考電壓設計:穩(wěn)定的參考電壓是ADC正常工作的基礎。在設計中,,應選用高精度的參考電壓源,,并合理設計其濾波和去耦電路,以減少噪聲和干擾,。信號調(diào)理:在ADC之前,,對輸入信號進行適當?shù)恼{(diào)理和濾波,以去除噪聲和干擾信號,,提高數(shù)據(jù)采集的精度和穩(wěn)定性。同時,,考慮信號的放大和衰減等處理,,以適應不同量程的輸入信號。 硬件產(chǎn)品研發(fā),,除了電子元器件成本,,還有什么成本?內(nèi)蒙古數(shù)據(jù)采集器硬件開發(fā)測試

硬件開發(fā)項目制定前需要考察項目的可持續(xù)性,。內(nèi)蒙古光伏硬件開發(fā)調(diào)試

現(xiàn)代化硬件設計的能效優(yōu)化策略隨著科技的飛速發(fā)展,,現(xiàn)代化硬件設計不再追求高性能,能效優(yōu)化也成為了不可忽視的重要方面,。能效優(yōu)化不*有助于減少能源消耗,,降低運行成本,還能提升設備的可持續(xù)性和環(huán)保性,。以下是一些關鍵的能效優(yōu)化策略,。1.先進制程技術的應用:采用更先進的半導體制程技術,如7nm,、5nm乃至更小的制程,,可以減少芯片內(nèi)部的漏電功耗,提高晶體管的開關速度,,從而在保持或提升性能的同時,,大幅降低功耗。2.動態(tài)電壓與頻率調(diào)整(DVFS):根據(jù)當前工作負載動態(tài)調(diào)整處理器的電壓和頻率,,可以在保證任務按時完成的前提下,,減少不必要的功耗,。這種技術廣泛應用于現(xiàn)代CPU和GPU設計中。3.低功耗設計與電源管理:通過低功耗電路設計,、智能電源管理策略(如自動休眠,、喚醒機制)以及高效的電源轉換技術(如DC-DC轉換器),可以進一步降低設備的整體功耗,。 內(nèi)蒙古光伏硬件開發(fā)調(diào)試

- 江蘇分析儀器設備硬件開發(fā)需求 2024-12-19

- 福建風力發(fā)電硬件開發(fā)注意事項 2024-12-19

- 山東檢測儀器設備硬件開發(fā)測試 2024-12-19

- 北京汽車新能源硬件開發(fā)環(huán)境 2024-12-18

- 江西電子科技產(chǎn)品硬件開發(fā)環(huán)境 2024-12-18

- 江西電子科技產(chǎn)品硬件開發(fā)管理規(guī)范 2024-12-18

- 浙江儲能設備硬件開發(fā)測試 2024-12-17

- 數(shù)據(jù)采集器硬件開發(fā)應用 2024-12-17

- 江西硬件開發(fā)費用 2024-12-17

- 內(nèi)蒙古檢測儀器設備硬件開發(fā)分類 2024-12-16

- 寧波電子影像儀直銷價格 2025-06-23

- 重慶流量儀表選型 2025-06-23

- 蘇州投影儀鏡片工廠 2025-06-23

- 新型明渠流量計廠家直銷 2025-06-23

- 金山區(qū)現(xiàn)代負載保持閥安裝 2025-06-23

- 南通現(xiàn)代液相色譜銷售 2025-06-23

- 廣西高速響應放大器系統(tǒng) 2025-06-23

- 江西DN25隔膜壓力表品牌 2025-06-23

- 江蘇 三箱式高低溫試驗箱哪家好 2025-06-23

- 安徽手持電橋型號 2025-06-23