內(nèi)蒙古智能設備硬件開發(fā)環(huán)境

硬件供應鏈與降低成本的挑戰(zhàn)標題:硬件供應鏈與降低成本的困境在硬件開發(fā)過程中,,供應鏈管理和降低成本是另外兩個重要的難點,。隨著全球化的發(fā)展,,硬件供應鏈變得越來越復雜和不可預測,,這給開發(fā)者帶來了巨大的挑戰(zhàn),。首先,,硬件供應鏈的可靠性是一個關鍵問題,。由于硬件系統(tǒng)包含多個組件和模塊,,這些組件和模塊往往來自不同的供應商和地區(qū)。因此,,開發(fā)者需要建立穩(wěn)定的供應鏈關系,,確保組件和模塊的供應及時、可靠,。然而,,在實際操作中,由于各種不可預見因素的影響,,供應鏈的可靠性往往難以保證,。其次,硬件降低成本也是一個難題,。隨著技術的不斷進步和市場競爭的加劇,,硬件成本不斷下降。然而,,在保證產(chǎn)品性能和質(zhì)量的前提下降低成本并非易事,。開發(fā)者需要在設計階段就進行成本優(yōu)化和降低成本,同時還需要在供應鏈管理中與供應商進行深入的談判和合作,。此外,,硬件開發(fā)的周期性和更新?lián)Q代也給降低成本帶來了挑戰(zhàn)。由于技術更新迅速,,硬件產(chǎn)品往往需要在短時間內(nèi)完成從設計到量產(chǎn)的全過程,。這要求開發(fā)者在有限的時間內(nèi)完成大量的工作,并在保證質(zhì)量的前提下降低成本,。因此,,如何平衡時間、質(zhì)量和成本之間的關系,,成為了硬件開發(fā)者必須面對的問題,。 方案公司是如何做硬件開發(fā)的?內(nèi)蒙古智能設備硬件開發(fā)環(huán)境

硬件開發(fā)

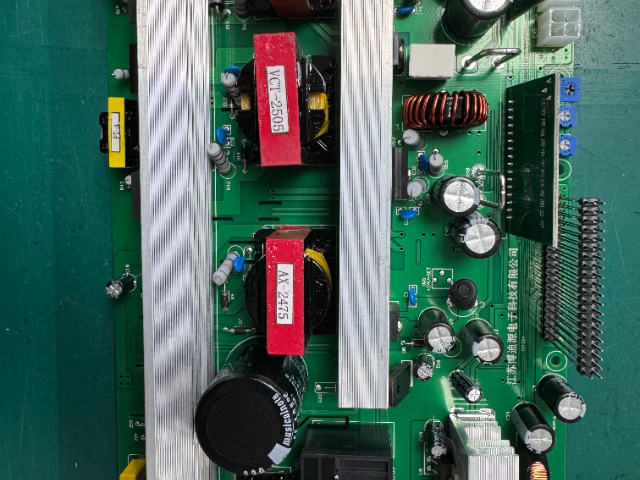

物聯(lián)網(wǎng)硬件開發(fā)的要點涉及多個方面:一,、技術選型1.傳感器技術傳感器是物聯(lián)網(wǎng)硬件開發(fā)中的關鍵器件,,用于檢測和攝取環(huán)境中的各種信息。2.射頻識別(RFID)技術RFID技術是一種無接觸的自動識別技術,,利用射頻信號及其空間耦合傳輸特性,,實現(xiàn)對靜態(tài)或移動待識別物體的自動識別。3.嵌入式系統(tǒng)技術嵌入式系統(tǒng)是物聯(lián)網(wǎng)設備的硬件和軟件系統(tǒng)基礎,。4.通信協(xié)議與網(wǎng)絡技術通信協(xié)議和網(wǎng)絡技術是物聯(lián)網(wǎng)硬件開發(fā)中不可或缺的部分,。二、設計優(yōu)化1.模塊化設計模塊化設計是物聯(lián)網(wǎng)硬件開發(fā)中的一種重要方法,。2.功耗管理物聯(lián)網(wǎng)設備通常需要在長時間內(nèi)持續(xù)運行,,因此功耗管理成為了一個重要問題,。3.安全性設計物聯(lián)網(wǎng)設備的安全性問題日益受到關注。三,、質(zhì)量控制物聯(lián)網(wǎng)硬件的質(zhì)量控制是確保設備性能和可靠性的重要環(huán)節(jié),。在開發(fā)過程中,需要建立完善的質(zhì)量管理體系,,對硬件的每一個環(huán)節(jié)進行嚴格的質(zhì)量控制,,包括原材料采購、生產(chǎn)過程,、測試驗證等,。四、供應鏈管理物聯(lián)網(wǎng)硬件的供應鏈管理對于確保產(chǎn)品的供應和質(zhì)量至關重要,。企業(yè)需要與供應商建立長期穩(wěn)定的合作關系,,并加強對供應商的管理和評估,以確保原材料和零部件的質(zhì)量和供應的穩(wěn)定性,。 江西汽車新能源硬件開發(fā)周期設計電源電路之前,,要對系統(tǒng)中各器件所需電源的需求情況進行分析。

FPGA(Field-ProgrammableGateArray,,現(xiàn)場可編程門陣列)硬件設計是一個復雜但高度靈活的過程,,它允許工程師通過編程來配置FPGA芯片以實現(xiàn)特定的數(shù)字電路功能。以下是對FPGA硬件設計流程的詳細解析:一,、FPGA硬件設計流程概述FPGA硬件設計流程主要包括以下幾個關鍵步驟:需求分析,、FPGA芯片選擇、硬件框圖設計,、HDL編程,、仿真測試、布局布線,、配置與調(diào)試,。二、具體步驟詳解需求分析確定FPGA的應用需求,,包括功能需求,、性能需求、成本預算等,。根據(jù)需求確定FPGA板卡的尺寸,、工作頻率、IO口數(shù)量,、運行環(huán)境等設計規(guī)格,。三、FPGA硬件設計工具在FPGA硬件設計過程中,,需要使用一系列工具來輔助完成各個步驟,。這些工具通常包括:IDE(集成開發(fā)環(huán)境):如Xilinx的Vivado和Intel的QuartusPrime,,它們集成了代碼編輯、綜合,、仿真和調(diào)試等功能,,能夠提高設計效率,。HDL編輯器:用于編寫和編輯HDL代碼,。仿真工具:如ModelSim,用于對HDL代碼進行功能仿真和時序仿真,。布局布線工具:負責將HDL代碼翻譯成物理電路圖,,并進行布局和布線。四,、FPGA硬件設計的優(yōu)勢FPGA硬件設計具有以下幾個優(yōu)勢:靈活性:FPGA可以通過編程來配置不同的電路功能,,具有很高的靈活性。

硬件開發(fā)和算法優(yōu)化之間存在著緊密而復雜的關系,。這種關系主要體現(xiàn)在以下幾個方面:一,、相互依存算法需要硬件支持:算法是解決問題的步驟和規(guī)則,但它本身無法直接執(zhí)行,。算法需要依賴硬件平臺來運行和實現(xiàn)其功能,。硬件為算法提供了必要的計算資源、存儲資源和通信接口,,使得算法能夠在實際環(huán)境中得到應用,。二、相互促進硬件發(fā)展推動算法創(chuàng)新:隨著硬件技術的不斷進步,,如處理器速度的提升,、內(nèi)存容量的擴大、新型存儲技術的出現(xiàn)等,,人們可以設計和實現(xiàn)更復雜,、更高效的算法。這些算法能夠充分利用硬件的性能優(yōu)勢,,解決更加復雜和大規(guī)模的問題,。算法優(yōu)化促進硬件利用:通過對算法的優(yōu)化,可以減少計算復雜度,、降低存儲需求,、提高數(shù)據(jù)處理速度等,,從而減輕硬件的負擔,,提高硬件的利用率。例如,,在深度學習領域,,通過優(yōu)化神經(jīng)網(wǎng)絡結(jié)構(gòu)和訓練算法,,可以減少計算資源的消耗,,使得深度學習模型能夠在硬件平臺上得到部署和應用。三,、協(xié)同工作硬件設計考慮算法需求:在硬件開發(fā)過程中,,需要充分考慮算法的需求和特性。 成功的硬件設計,,主要功能的實現(xiàn)只是所有環(huán)節(jié)中的一小部分,。

硬件開發(fā)的學習順序可以根據(jù)不同的學習目標和背景進行調(diào)整,但以下是一個較為通用的學習路徑,,涵蓋了從基礎知識到技能的逐步深入:一,、基礎知識學習電路與電子基礎學習基本的電路理論,包括電流,、電壓,、電阻、電容,、電感等基本概念,。理解模擬電路和數(shù)字電路的基本原理,學習電路分析方法和設計技巧二,、嵌入式系統(tǒng)開發(fā)單片機學習從簡單的單片機(如51單片機)入手,,學習其基本結(jié)構(gòu)、工作原理和編程方法,。通過開發(fā)板實踐,,編寫簡單的程序,如流水燈,、按鍵掃描等,,理解單片機設備的交互。三,、硬件設計與開發(fā)硬件描述語言(HDL)學習VHDL或Verilog等硬件描述語言,,用于描述和模擬數(shù)字電路。通過HDL進行電路設計,、驗證,,提高設計效率和質(zhì)量。電路設計軟件學習使用電路設計軟件(如AltiumDesigner,、Cadence等)進行電路原理圖和PCB設計,。掌握PCB布局布線技巧,進行電路板的設計和制作,。四,、系統(tǒng)級設計與開發(fā)嵌入式操作系統(tǒng)學習嵌入式操作系統(tǒng)的基本原理和架構(gòu),如Linux,、RTOS等,。掌握操作系統(tǒng)的移植,、裁剪和驅(qū)動開發(fā)等技能。硬件開發(fā)流程對硬件開發(fā)的全過程進行了科學分解,,規(guī)范了硬件開發(fā)的五大任務,。安徽電力設備硬件開發(fā)平均價格

硬件設計利用FPGA和USB接口芯片結(jié)合的方案,具有功耗低,、時鐘頻率高,、速度快、效率高等特點,。內(nèi)蒙古智能設備硬件開發(fā)環(huán)境

FPGA(Field-ProgrammableGateArray,,現(xiàn)場可編程門陣列)硬件設計雖然具有諸多優(yōu)勢,,如高靈活性,、高性能、低功耗等,,但也存在一些缺點,。1.成本高設計成本:FPGA芯片的設計和開發(fā)需要較高的技術投入和復雜的工程流程,包括硬件描述語言(HDL)編程,、仿真,、綜合、布局布線等多個步驟,,這些都需要專業(yè)的工程師和昂貴的開發(fā)工具,。2.硬件資源有限邏輯資源限制:FPGA芯片內(nèi)部包含一定數(shù)量的邏輯塊、IO接口,、存儲資源等,,這些資源是有限的。在設計復雜的系統(tǒng)時,,可能會遇到資源不足的問題,,需要優(yōu)化設計或選擇更高性能的FPGA芯片.3.時序設計復雜時鐘管理:FPGA的時鐘管理相對復雜,需要仔細設計和設置時鐘域,、時鐘同步,、時鐘分頻等。4.開發(fā)周期長設計驗證:FPGA設計需要經(jīng)過多個階段的驗證,,包括功能驗證,、時序驗證、物理驗證等,。5.技術門檻高專業(yè)知識要求:FPGA設計需要掌握硬件描述語言,、數(shù)字電路設計、計算機架構(gòu)等多方面的知識,。這些知識的獲取和掌握需要較長的時間和努力,。人才短缺:由于FPGA技術的專業(yè)性和復雜性,,相關人才相對短缺。這可能導致項目在招聘和團隊建設方面遇到困難,。 內(nèi)蒙古智能設備硬件開發(fā)環(huán)境

- 江蘇分析儀器設備硬件開發(fā)需求 2024-12-19

- 福建風力發(fā)電硬件開發(fā)注意事項 2024-12-19

- 山東檢測儀器設備硬件開發(fā)測試 2024-12-19

- 北京汽車新能源硬件開發(fā)環(huán)境 2024-12-18

- 江西電子科技產(chǎn)品硬件開發(fā)環(huán)境 2024-12-18

- 江西電子科技產(chǎn)品硬件開發(fā)管理規(guī)范 2024-12-18

- 浙江儲能設備硬件開發(fā)測試 2024-12-17

- 數(shù)據(jù)采集器硬件開發(fā)應用 2024-12-17

- 江西硬件開發(fā)費用 2024-12-17

- 內(nèi)蒙古檢測儀器設備硬件開發(fā)分類 2024-12-16

- 杭州鎢燈絲掃描電子顯微鏡應用 2025-06-23

- 河南淋雨試驗室直銷 2025-06-23

- 揭陽固定鏡頭相機鏡片選擇 2025-06-23

- 廣東MES信息化系統(tǒng) 2025-06-23

- 揚州天然氣客服調(diào)度管理系統(tǒng)價格 2025-06-23

- 江蘇球閥維修 2025-06-23

- 管道泵激光對中廠家 2025-06-23

- 杭州微孔板酶標儀毒性檢測 2025-06-23

- 浙江多參量錒力巴流量計品牌 2025-06-23

- 福建接觸角測量儀24小時服務 2025-06-23