隨州高速PCB制板價(jià)格大全

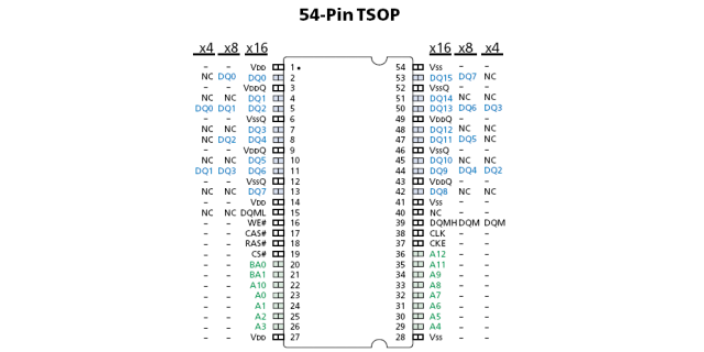

選擇從器件廠商那里得到的IBIS模型即可模型設(shè)置完成后選擇OK,,退出圖82)在圖6所示的窗口,,選擇左下角的UpdateModelsinSchematic,,將修改后的模型更新到原理圖中,。3)在圖6所示的窗口,,選擇右下角的AnalyzeDesign…,在彈出的窗口中(圖10)保留缺省值,,然后點(diǎn)擊AnalyzeDesign選項(xiàng),,系統(tǒng)開(kāi)始進(jìn)行分析。4)圖11為分析后的網(wǎng)絡(luò)狀態(tài)窗口,,通過(guò)此窗口中左側(cè)部分可以看到網(wǎng)絡(luò)是否通過(guò)了相應(yīng)的規(guī)則,,如過(guò)沖幅度等,通過(guò)右側(cè)的設(shè)置,,可以以圖形的方式顯示過(guò)沖和串?dāng)_結(jié)果,。選擇左側(cè)其中一個(gè)網(wǎng)絡(luò)TXB,右鍵點(diǎn)擊,,在下拉菜單中選擇Details…,,在彈出的如圖12所示的窗口中可以看到針對(duì)此網(wǎng)絡(luò)分析的詳細(xì)信息。圖10圖11圖125)下面以圖形的方式進(jìn)行反射分析,,雙擊需要分析的網(wǎng)絡(luò)TXB,,將其導(dǎo)入到窗口的右側(cè)如圖13所示。圖13*選擇窗13口右下角的Reflections…,,反射分析的波形結(jié)果將會(huì)顯示出來(lái)如圖14圖14右鍵點(diǎn)擊A和CursorB,,然后可以利用它們來(lái)測(cè)量確切的參數(shù)。測(cè)量結(jié)果在SimData窗口如圖16所示,。圖15圖166)返回到圖11所示的界面下,,窗口右側(cè)給出了幾種端接的策略來(lái)減小反射所帶來(lái)的影響,,選擇SerialRes如圖18所示,將最小值和最大值分別設(shè)置為25和125,,選中PerformSweep選項(xiàng),。軟板動(dòng)態(tài)測(cè)試:10萬(wàn)次彎折實(shí)驗(yàn),柔性電路壽命保障,。隨州高速PCB制板價(jià)格大全

PCB(印刷電路板)制版是現(xiàn)代電子產(chǎn)品設(shè)計(jì)和制造中不可或缺的重要環(huán)節(jié),。隨著科技的飛速發(fā)展,電子設(shè)備的性能不斷提升,,對(duì)電路板的要求也日益嚴(yán)格,。PCB制版不僅涉及到電路布局的合理性,更關(guān)乎到產(chǎn)品的穩(wěn)定性和可靠性,。在PCB制版的過(guò)程中,,首先需要進(jìn)行電路設(shè)計(jì)。在這個(gè)階段,,工程師們會(huì)利用專(zhuān)業(yè)軟件繪制出電路圖,,標(biāo)明各個(gè)元器件之間的連接關(guān)系。設(shè)計(jì)完成后,,電路圖將被轉(zhuǎn)化為PCB布局圖,,此時(shí)需要充分考慮到各個(gè)元器件的位置、走線的長(zhǎng)度以及信號(hào)的分布等因素,,以確保電路的高效運(yùn)行,。接下來(lái),,進(jìn)入了PCB的實(shí)際制版環(huán)節(jié),。通過(guò)光刻技術(shù),將設(shè)計(jì)好的圖案轉(zhuǎn)移到覆銅板上,,這一過(guò)程需要高度的精確性和工藝控制,。黃岡生產(chǎn)PCB制板批發(fā)3D打印樣板:48小時(shí)立體電路成型,驗(yàn)證設(shè)計(jì)零等待,。

有利于元器件之間的布線工作,,但是該方案的缺陷也較為明顯,表現(xiàn)為以下兩方面,。①電源層和地線層分隔較遠(yuǎn),,沒(méi)有充分耦合。②信號(hào)層Siganl_2(Inner_2)和Siganl_3(Inner_3)直接相鄰,,信號(hào)隔離性不好,,容易發(fā)生串?dāng)_。(2)Siganl_1(Top),,Siganl_2(Inner_1),,POWER(Inner_2),,GND(Inner_3),Siganl_3(Inner_4),,Siganl_4(Bottom),。方案2相對(duì)于方案1,電源層和地線層有了充分的耦合,,比方案1有一定的優(yōu)勢(shì),,但是Siganl_1(Top)和Siganl_2(Inner_1)以及Siganl_3(Inner_4)和Siganl_4(Bottom)信號(hào)層直接相鄰,信號(hào)隔離不好,,容易發(fā)生串?dāng)_的問(wèn)題并沒(méi)有得到解決,。(3)Siganl_1(Top),GND(Inner_1),,Siganl_2(Inner_2),,POWER(Inner_3),GND(Inner_4),,Siganl_3(Bottom),。相對(duì)于方案1和方案2,方案3減少了一個(gè)信號(hào)層,,多了一個(gè)內(nèi)電層,,雖然可供布線的層面減少了,但是該方案解決了方案1和方案2共有的缺陷,。①電源層和地線層緊密耦合,。②每個(gè)信號(hào)層都與內(nèi)電層直接相鄰,與其他信號(hào)層均有有效的隔離,,不易發(fā)生串?dāng)_,。③Siganl_2(Inner_2)和兩個(gè)內(nèi)電層GND(Inner_1)和POWER(Inner_3)相鄰,可以用來(lái)傳輸高速信號(hào),。

PCBA貼片不良原因分析發(fā)布時(shí)間:2020-01-03編輯作者:金致卓閱讀:447PCBA貼片生產(chǎn)過(guò)程中,,由于操作失誤的影響,容易導(dǎo)致PCBA貼片的不良,,如:空焊,,短路,翹立,缺件,,錫珠,,翹腳,浮高,,錯(cuò)件,,冷焊,反向,反白/反面,,偏移,,元件破損,,少錫,多錫,,金手指粘錫,,溢膠等,需要對(duì)這些不良開(kāi)展分析,,并開(kāi)展改進(jìn),,提高產(chǎn)品品質(zhì)。一,、空焊紅膠特異性較弱,;網(wǎng)板開(kāi)孔不佳;銅鉑間距過(guò)大或大銅貼小元件,;刮刀壓力大,;元件平整度不佳(翹腳,變形)回焊爐預(yù)熱區(qū)升溫太快;PCB銅鉑太臟或是氧化,;PCB板含有水分,;機(jī)器貼片偏移;紅膠印刷偏移,;機(jī)器夾板軌道松動(dòng)導(dǎo)致貼片偏移,;MARK點(diǎn)誤照導(dǎo)致元件打偏,導(dǎo)致空焊,;二,、短路網(wǎng)板與PCB板間距過(guò)大導(dǎo)致紅膠印刷過(guò)厚短路;元件貼片高度設(shè)置過(guò)低將紅膠擠壓導(dǎo)致短路,;回焊爐升溫過(guò)快導(dǎo)致,;元件貼片偏移導(dǎo)致;網(wǎng)板開(kāi)孔不佳(厚度過(guò)厚,,引腳開(kāi)孔過(guò)長(zhǎng),,開(kāi)孔過(guò)大),;紅膠沒(méi)法承受元件重量,;網(wǎng)板或刮刀變形導(dǎo)致紅膠印刷過(guò)厚;紅膠特異性較強(qiáng),;空貼點(diǎn)位封貼膠紙卷起導(dǎo)致周邊元件紅膠印刷過(guò)厚,;回流焊振動(dòng)過(guò)大或不水平;三,、翹立銅鉑兩邊大小不一造成拉力不勻,;預(yù)熱升溫速率太快;機(jī)器貼片偏移,;紅膠印刷厚度均,;回焊爐內(nèi)溫度分布不勻,;紅膠印刷偏移。PCB制板不僅能滿足客戶的需求,,更能在激烈的市場(chǎng)競(jìng)爭(zhēng)中脫穎而出,。

AltiumDesigner要求必須建立一個(gè)工程項(xiàng)目名稱(chēng)。在原理圖SI分析中,,系統(tǒng)將采用在SISetupOption對(duì)話框設(shè)置的傳輸線平均線長(zhǎng)和特征阻抗值,;仿真器也將直接采用規(guī)則設(shè)置中信號(hào)完整性規(guī)則約束,如激勵(lì)源和供電網(wǎng)絡(luò)等,,同時(shí),,允許用戶直接在原理圖編輯環(huán)境下放置PCBLayout圖標(biāo),直接對(duì)原理圖內(nèi)網(wǎng)絡(luò)定義規(guī)則約束,。當(dāng)建立了必要的仿真模型后,,在原理圖編輯環(huán)境的菜單中選擇Tools->SignalIntegrity命令,運(yùn)行仿真,。b.布線后(即PCB版圖設(shè)計(jì)階段)SI分析概述用戶如需對(duì)項(xiàng)目PCB版圖設(shè)計(jì)進(jìn)行SI仿真分析,,AltiumDesigner要求必須在項(xiàng)目工程中建立相關(guān)的原理圖設(shè)計(jì)。此時(shí),,當(dāng)用戶在任何一個(gè)原理圖文檔下運(yùn)行SI分析功能將與PCB版圖設(shè)計(jì)下允許SI分析功能得到相同的結(jié)果,。當(dāng)建立了必要的仿真模型后,在PCB編輯環(huán)境的菜單中選擇Tools->SignalIntegrity命令,,運(yùn)行仿真,。4,操作實(shí)例:1)在AltiumDesigner的Protel設(shè)計(jì)環(huán)境下,,選擇File\OpenProject,選擇安裝目錄下\Examples\ReferenceDesign\4PortSerialInterface\4PortSerial,,進(jìn)入PCB編輯環(huán)境,如下圖1.圖1在PCB文件中進(jìn)行SI分析選擇Design/LayerStackManager…,,配置好相應(yīng)的層后,,選擇ImpedanceCalculation…。PCB制板作為電路設(shè)計(jì)與制造的重要環(huán)節(jié),,扮演著至關(guān)重要的角色,。黃岡焊接PCB制板價(jià)格大全

阻抗條隨板測(cè)試:實(shí)時(shí)監(jiān)控阻抗值,確保批量一致性,。隨州高速PCB制板價(jià)格大全

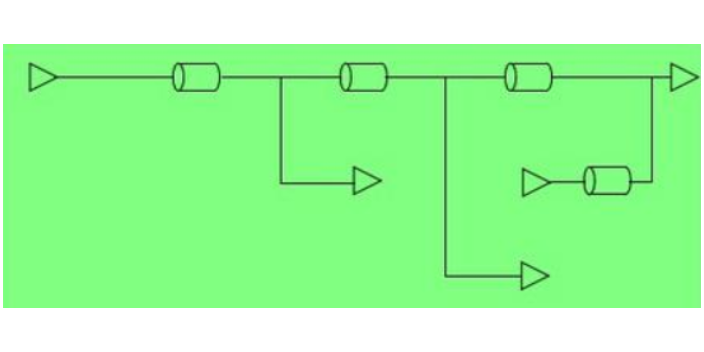

在高速數(shù)字系統(tǒng)中,,由于脈沖上升/下降時(shí)間通常在10到幾百p秒,當(dāng)受到諸如內(nèi)連,、傳輸時(shí)延和電源噪聲等因素的影響,,從而造成脈沖信號(hào)失真的現(xiàn)象;在自然界中,存在著各種各樣頻率的微波和電磁干擾源,,可能由于很小的差異導(dǎo)致高速系統(tǒng)設(shè)計(jì)的失?。辉陔娮赢a(chǎn)品向高密和高速電路設(shè)計(jì)方向發(fā)展,,解決一系列信號(hào)完整性的問(wèn)題,,成為當(dāng)前每一個(gè)電子設(shè)計(jì)者所必須面對(duì)的問(wèn)題。業(yè)界通常會(huì)采用在PCB制板前期,,通過(guò)信號(hào)完整性分析工具盡可能將設(shè)計(jì)風(fēng)險(xiǎn)降,,從而也促進(jìn)了EDA設(shè)計(jì)工具的發(fā)展……信號(hào)完整性(SignalIntegrity,簡(jiǎn)稱(chēng)SI)問(wèn)題是指高速數(shù)字電路中,,脈沖形狀畸變而引發(fā)的信號(hào)失真問(wèn)題,,通常由傳輸線阻抗不匹配產(chǎn)生的問(wèn)題。而影響阻抗匹配的因素包括信號(hào)源的架構(gòu),、輸出阻抗(outputimpedance),、走線的特性阻抗、負(fù)載端的特性,、走線的拓樸(topology)架構(gòu)等,。解決的方式可以采用端接(termination)與調(diào)整走線拓樸的策略。信號(hào)完整性問(wèn)題通常不是由某個(gè)單一因素導(dǎo)致的,,而是板級(jí)設(shè)計(jì)中多種因素共同作用的結(jié)果,。信號(hào)完整性問(wèn)題主要表現(xiàn)形式包括信號(hào)反射、信號(hào)振鈴,、地彈,、串?dāng)_等;1,,AltiumDesigner信號(hào)完整性分析(機(jī)理,、模型、功能)在AltiumDesigner設(shè)計(jì)環(huán)境下,。隨州高速PCB制板價(jià)格大全

- 黃石PCB制版多少錢(qián) 2025-05-14

- 荊州印制PCB制板報(bào)價(jià) 2025-05-14

- 了解PCB培訓(xùn)批發(fā) 2025-05-14

- 武漢了解PCB制版多少錢(qián) 2025-05-14

- 武漢定制PCB制版 2025-05-14

- 荊門(mén)設(shè)計(jì)PCB制版功能 2025-05-14

- 湖北高速PCB培訓(xùn)怎么樣 2025-05-14

- 湖北正規(guī)PCB培訓(xùn)布局 2025-05-14

- 武漢打造PCB培訓(xùn)銷(xiāo)售電話 2025-05-14

- 武漢設(shè)計(jì)PCB制版多少錢(qián) 2025-05-14

- 原裝進(jìn)口電容耐壓測(cè)試儀批發(fā) 2025-05-14

- 物流分揀直流無(wú)刷驅(qū)動(dòng)器批發(fā) 2025-05-14

- 重慶WeidmullerSAKDU2.5N接插件 2025-05-14

- 靜安區(qū)出口儀器儀表銷(xiāo)售降價(jià) 2025-05-14

- 工業(yè)園區(qū)特色石無(wú)鉛價(jià)格 2025-05-14

- 湖南新能源電纜經(jīng)銷(xiāo)商 2025-05-14

- 山西光伏鋁合金導(dǎo)軌費(fèi)用 2025-05-14

- 汕尾酒店客控智能方案費(fèi)用 2025-05-14

- 南京進(jìn)口電子絕緣材料廠家現(xiàn)貨 2025-05-14

- 杭州負(fù)壓式加氯機(jī)價(jià)格 2025-05-14