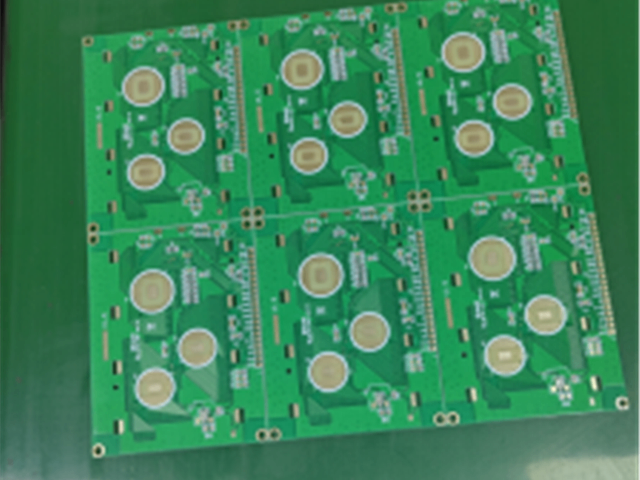

深圳龍崗區(qū)立式PCB貼片報(bào)價(jià)

PCB的制造過程通常包括以下幾個(gè)步驟:1.設(shè)計(jì):首先,根據(jù)電路設(shè)計(jì)需求,使用電路設(shè)計(jì)軟件進(jìn)行電路圖設(shè)計(jì)和布局設(shè)計(jì),。設(shè)計(jì)完成后,,生成Gerber文件,包含了電路板的各個(gè)層次的信息,。2.印刷:將Gerber文件提供給PCB制造商,制造商會(huì)使用光刻技術(shù)將Gerber文件上的電路圖案轉(zhuǎn)移到光刻膜上。然后,,將光刻膜覆蓋在銅箔上,通過化學(xué)腐蝕去除未被光刻膜保護(hù)的銅箔,,形成電路圖案,。3.鉆孔:在印刷好的電路板上進(jìn)行鉆孔,用于安裝元件和連接電路,。鉆孔通常使用CNC鉆床進(jìn)行,,根據(jù)設(shè)計(jì)要求進(jìn)行鉆孔。4.電鍍:在鉆孔完成后,,需要對(duì)電路板進(jìn)行電鍍處理,,以增加電路板的導(dǎo)電性。首先,,在電路板表面涂上一層化學(xué)鍍銅,,然后通過電解過程將銅沉積在鉆孔內(nèi)壁和電路圖案上。5.焊接:將元件焊接到電路板上,。這可以通過手工焊接或使用自動(dòng)化設(shè)備進(jìn)行,。焊接可以使用表面貼裝技術(shù)(SMT)或插件技術(shù)(THT)進(jìn)行。6.測(cè)試:完成焊接后,,對(duì)電路板進(jìn)行功能測(cè)試和電氣測(cè)試,,以確保電路板的正常工作。7.組裝:如果需要,,將電路板與其他組件(如插座,、開關(guān)等)進(jìn)行組裝,以完成產(chǎn)品,。8.檢驗(yàn):對(duì)組裝好的產(chǎn)品進(jìn)行檢驗(yàn),,確保產(chǎn)品符合質(zhì)量標(biāo)準(zhǔn),。PCB廣泛應(yīng)用于電子設(shè)備中,如計(jì)算機(jī),、手機(jī),、電視等。深圳龍崗區(qū)立式PCB貼片報(bào)價(jià)

PCB的高速信號(hào)傳輸和時(shí)鐘分配面臨以下挑戰(zhàn):1.信號(hào)完整性:高速信號(hào)傳輸需要考慮信號(hào)的完整性,,包括信號(hào)的傳輸延遲,、時(shí)鐘抖動(dòng)、串?dāng)_等問題,。這些問題可能導(dǎo)致信號(hào)失真,、時(shí)序錯(cuò)誤等。2.信號(hào)耦合和串?dāng)_:在高速信號(hào)傳輸中,,不同信號(hào)之間可能會(huì)發(fā)生耦合和串?dāng)_現(xiàn)象,,導(dǎo)致信號(hào)失真。這需要采取合適的布局和屏蔽措施來減少耦合和串?dāng)_,。3.時(shí)鐘分配:在設(shè)計(jì)中,,時(shí)鐘信號(hào)的分配是一個(gè)關(guān)鍵問題。時(shí)鐘信號(hào)的傳輸延遲和抖動(dòng)可能會(huì)導(dǎo)致時(shí)序錯(cuò)誤和系統(tǒng)性能下降,。因此,,需要合理規(guī)劃時(shí)鐘分配路徑,減少時(shí)鐘信號(hào)的傳輸延遲和抖動(dòng),。4.信號(hào)完整性分析:在高速信號(hào)傳輸中,,需要進(jìn)行信號(hào)完整性分析,包括時(shí)序分析,、電磁兼容性分析等,。這些分析可以幫助設(shè)計(jì)人員發(fā)現(xiàn)潛在的問題,并采取相應(yīng)的措施來解決,。5.材料選擇和層間堆疊:在高速信號(hào)傳輸中,,選擇合適的材料和層間堆疊方式對(duì)信號(hào)完整性至關(guān)重要。不同材料和層間堆疊方式會(huì)對(duì)信號(hào)傳輸特性產(chǎn)生影響,,需要進(jìn)行合適的仿真和測(cè)試來選擇更好的方案,。6.電源和地線分配:在高速信號(hào)傳輸中,電源和地線的分配也是一個(gè)重要問題,。合理的電源和地線分配可以減少信號(hào)噪聲和串?dāng)_,提高系統(tǒng)性能,。濟(jì)南電路PCB貼片PCB的制造過程中,,可以采用高精度的光刻技術(shù),實(shí)現(xiàn)微細(xì)線路和小尺寸元件的布局,。

PCB的成本因素主要包括以下幾個(gè)方面:1.材料成本:包括基板材料,、導(dǎo)電層材料,、阻抗控制材料等。2.工藝成本:包括制造工藝,、印刷,、蝕刻、鉆孔,、貼片等工藝的成本,。3.設(shè)計(jì)成本:包括PCB設(shè)計(jì)軟件的使用費(fèi)用、設(shè)計(jì)人員的工資等,。4.測(cè)試成本:包括PCB的功能測(cè)試,、可靠性測(cè)試等。為了降低PCB的制造成本,,可以采取以下措施:1.選擇合適的材料:選擇成本較低的材料,,如常見的FR.4基板材料,避免使用高成本的特殊材料,。2.優(yōu)化設(shè)計(jì):合理布局和布線,,減少板層數(shù),降低難度和成本,。3.提高產(chǎn)能利用率:合理安排生產(chǎn)計(jì)劃,,提高生產(chǎn)效率,減少生產(chǎn)時(shí)間和成本,。4.選擇合適的工廠:選擇有經(jīng)驗(yàn),、設(shè)備先進(jìn)、成本較低的PCB制造廠商,,進(jìn)行合理的報(bào)價(jià)和談判,。5.優(yōu)化工藝流程:采用先進(jìn)的制造工藝和設(shè)備,提高生產(chǎn)效率和質(zhì)量,,降低成本,。6.合理控制測(cè)試成本:根據(jù)產(chǎn)品的需求和要求,合理選擇測(cè)試項(xiàng)目和方法,,避免不必要的測(cè)試和成本,。

PCB的特點(diǎn)和應(yīng)用主要包括以下幾個(gè)方面:1.高密度:PCB具有高度集成的特點(diǎn),能夠在有限的空間內(nèi)實(shí)現(xiàn)復(fù)雜的電路布局,,滿足電子產(chǎn)品對(duì)于小型化和輕量化的需求,。2.可靠性:PCB具有良好的電氣性能和機(jī)械性能,能夠確保電子產(chǎn)品的穩(wěn)定性和可靠性,。3.生產(chǎn)效率高:PCB的生產(chǎn)過程可以實(shí)現(xiàn)自動(dòng)化和批量化,,能夠很大程度的提高生產(chǎn)效率和降低成本。4.應(yīng)用廣闊:PCB廣泛應(yīng)用于電子產(chǎn)品中,如計(jì)算機(jī),、手機(jī),、電視、汽車等,,是現(xiàn)代電子產(chǎn)品的重要組成部分,。PCB的材料包括基板、導(dǎo)電層,、絕緣層和焊盤等,。

PCB的阻抗控制和信號(hào)完整性是通過以下幾個(gè)方面來實(shí)現(xiàn)的:1.PCB設(shè)計(jì):在PCB設(shè)計(jì)過程中,需要考慮信號(hào)線的寬度,、間距,、層間距、層間引線等參數(shù),,以控制信號(hào)線的阻抗,。通過合理的布局和層間引線的設(shè)計(jì),可以減小信號(hào)線的串?dāng)_和反射,,提高信號(hào)的完整性,。2.PCB材料選擇:選擇合適的PCB材料也是實(shí)現(xiàn)阻抗控制和信號(hào)完整性的重要因素。不同的材料具有不同的介電常數(shù)和損耗因子,,會(huì)對(duì)信號(hào)的傳輸特性產(chǎn)生影響,。選擇低介電常數(shù)和低損耗因子的材料,可以減小信號(hào)的傳輸損耗和失真,。3.信號(hào)層分離:為了減小信號(hào)線之間的串?dāng)_,,可以將不同信號(hào)層分離開來,通過地層和電源層的設(shè)置,,形成屏蔽效果,,減小信號(hào)線之間的相互影響。4.信號(hào)線匹配:對(duì)于高速信號(hào)線,,需要進(jìn)行阻抗匹配,,以減小信號(hào)的反射和傳輸損耗。通過合理的信號(hào)線寬度和間距設(shè)計(jì),,可以使信號(hào)線的阻抗與驅(qū)動(dòng)源的阻抗匹配,,提高信號(hào)的傳輸質(zhì)量。5.信號(hào)線終端控制:在信號(hào)線的終端,,可以采用終端電阻,、電流源等方式來控制信號(hào)的阻抗。終端電阻可以減小信號(hào)的反射,,電流源可以提供穩(wěn)定的驅(qū)動(dòng)信號(hào),,提高信號(hào)的完整性。PCB的制造過程中,可以采用表面處理技術(shù),,如金屬化、防腐蝕等,,提高電路板的耐用性,。福州固定座PCB貼片生產(chǎn)商

PCB的制造過程中,可以采用綠色環(huán)保的工藝和材料,,減少對(duì)環(huán)境的影響,。深圳龍崗區(qū)立式PCB貼片報(bào)價(jià)

層間電容和層間電感是PCB中的兩個(gè)重要參數(shù),它們會(huì)對(duì)電路性能產(chǎn)生影響,。層間電容是指PCB中不同層之間的電容,。當(dāng)電流在PCB中流動(dòng)時(shí),由于層間電容的存在,,會(huì)導(dǎo)致電流的延遲和損耗,。層間電容越大,電流的延遲和損耗就越大,,從而影響電路的工作速度和信號(hào)傳輸質(zhì)量,。因此,設(shè)計(jì)PCB時(shí)需要盡量減小層間電容,,例如通過增加層間距離,、使用低介電常數(shù)的材料等方法。層間電感是指PCB中不同層之間的電感,。當(dāng)電流在PCB中流動(dòng)時(shí),,由于層間電感的存在,會(huì)產(chǎn)生電磁感應(yīng)現(xiàn)象,,導(dǎo)致電流的變化和噪聲,。層間電感越大,電流的變化和噪聲就越大,,從而影響電路的穩(wěn)定性和抗干擾能力,。因此,設(shè)計(jì)PCB時(shí)需要盡量減小層間電感,,例如通過增加層間距離,、使用低電感材料等方法。綜上所述,,層間電容和層間電感會(huì)影響電路的工作速度,、信號(hào)傳輸質(zhì)量、穩(wěn)定性和抗干擾能力,。在PCB設(shè)計(jì)中,,需要合理選擇材料和布局,以減小層間電容和層間電感,從而提高電路性能,。深圳龍崗區(qū)立式PCB貼片報(bào)價(jià)

- 武漢電子SMT貼片批發(fā)價(jià) 2025-04-27

- 濟(jì)南FPC貼片供應(yīng)商 2025-04-27

- 長(zhǎng)春可調(diào)式PCB貼片生產(chǎn)企業(yè) 2025-04-27

- 武漢電子SMT貼片公司 2025-04-27

- 南京手機(jī)SMT貼片生產(chǎn)公司 2025-04-27

- 西寧軟硬結(jié)合FPC貼片哪家好 2025-04-27

- 北京可調(diào)式PCB貼片供應(yīng)商 2025-04-27

- 蘇州PCB貼片生產(chǎn)商 2025-04-27

- 西寧加厚PCB貼片生產(chǎn)廠家 2025-04-27

- 深圳龍崗區(qū)雙面FPC貼片廠 2025-04-27

- 周邊如何定制HDI優(yōu)惠 2025-04-27

- 佛山低壓保險(xiǎn)絲座廠家價(jià)格 2025-04-27

- 內(nèi)蒙古寬帶調(diào)諧阻尼光學(xué)平臺(tái)Newport 2025-04-27

- GORE-AVS70-AMF300070卡扣式防水透氣閥代理商 2025-04-27

- 浙江耐扭式防水接頭廠家 2025-04-27

- 北京優(yōu)勢(shì)特種變壓器哪家好 2025-04-27

- 北京麥拉喇叭加工廠 2025-04-27

- 青海恩智浦穩(wěn)壓二極管 2025-04-27

- 遼寧風(fēng)速氣象數(shù)據(jù)下載 2025-04-27

- 汕頭高爾夫球車線束批發(fā) 2025-04-27