揭陽(yáng)PCIE分析儀電話

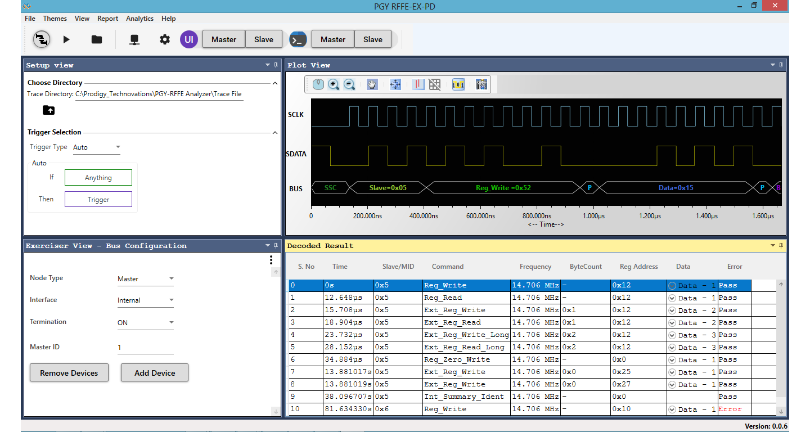

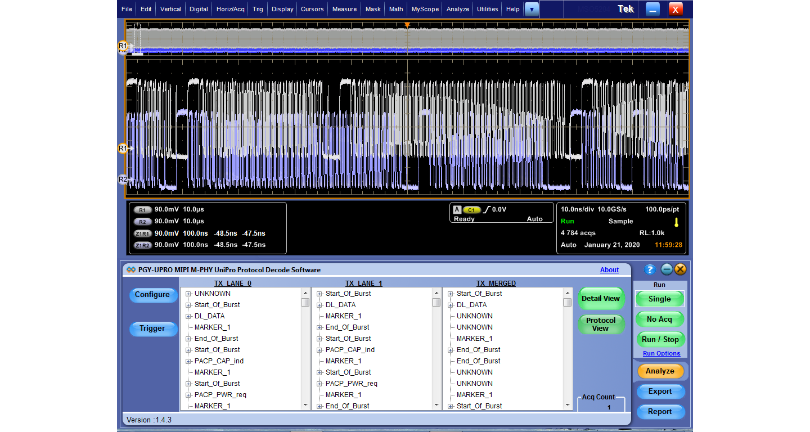

終比較結(jié)果將對(duì)“差分信號(hào)高于Vref還是低于Vref,?”的問題作出解答:對(duì)眼隙的eyescan測(cè)量是通過使用不同Vref設(shè)置進(jìn)行一系列eyefinder測(cè)量完成的,。差分信號(hào)的默認(rèn)eyefinder測(cè)量使用Vref=0V。通過將Vref增至零以上,。歐奧電子是Prodigy在中國(guó)區(qū)的官方授權(quán)合作伙伴,,ProdigyMPHY,UniPro,UFS總線協(xié)議分析儀測(cè)試解決方案不會(huì)收到EAR進(jìn)出口方面的管制。同時(shí)還有代理其他總類的協(xié)議分析儀,,包括嵌入式設(shè)備用的SDIO協(xié)議分析儀,QSPI協(xié)議分析儀及訓(xùn)練器,I3C協(xié)議分析儀及訓(xùn)練器,RFFE協(xié)議分析儀及訓(xùn)練器等等,。我司還有代理SPMI協(xié)議分析儀及訓(xùn)練器,車載以太網(wǎng)分析儀,以及各種相關(guān)的基于示波器的解碼軟件和SI測(cè)試軟件,。同時(shí),,歐奧電子也有提供高難度焊接,以及高速信號(hào),。如UFS,,DDR3/DDR4,USBtypeC等高速協(xié)議抓取和分析的服務(wù),。我們會(huì)找到信號(hào)與上升的Vref值交叉的位置,。如果Vref升至足夠高,信號(hào)的頂部軌跡將通過Vref,,我們便會(huì)看到眼的頂端,。再將Vref升高一點(diǎn)會(huì)導(dǎo)致Vcomp保持在Vlo,表示信號(hào)不會(huì)升至該電之,,將Vref移至零以下會(huì)看到眼的下半部,。eyescan/eyefinder顯示窗口會(huì)在每個(gè)信號(hào)的eyescan圖下方顯示eyefinder交疊部分,,以此顯示eyefinder與eyescan之間的這一關(guān)系,。SDIO邏輯分析儀/訓(xùn)練器廠家只找歐奧,服務(wù)好,!揭陽(yáng)PCIE分析儀電話

等在選擇內(nèi)存長(zhǎng)度時(shí)的基準(zhǔn)是"于我們即將觀測(cè)的系統(tǒng)可以進(jìn)行分割后的塊的長(zhǎng)度,。測(cè)試夾具邏輯分析儀通過探頭與被測(cè)器件連接,,測(cè)試夾具起著很重要的作用,測(cè)試夾具有很多種,,如飛行頭和蒼蠅頭等,。探頭邏輯分析儀通過探頭與被測(cè)器件連接,探頭起著信號(hào)接口的作用,,在保持信號(hào)完整性中占有重要位置,。邏輯分析儀與數(shù)字示波器不同,雖然相對(duì)上下限值的幅度變化并不重要,,但幅度失真一定會(huì)轉(zhuǎn)換成定時(shí)誤差,。邏輯分析儀具有幾十至幾百通道的探頭其頻率響應(yīng)從幾十至幾百M(fèi)Hz,保證各路探頭的相對(duì)延時(shí)小和保持幅度的失真較低。這是表征邏輯分析儀探頭性能的關(guān)鍵參數(shù),。Agilent公司的無源探頭和Tektronix公司的有源探頭具代表性,,屬于邏輯分析儀的探頭。邏輯分析儀的強(qiáng)項(xiàng)在于能洞察許多信道中信號(hào)的定時(shí)關(guān)系,??上У氖牵绻鱾€(gè)通道之間略有差別便會(huì)產(chǎn)生通道的定時(shí)偏差,,在某些型號(hào)的邏輯分析儀里,,這種偏差能減小到小,但是仍有殘留值存在,。通用邏輯分析儀,,如Tektronix公司的TLA600型或Agilent公司的HP16600型,在所有通道中的時(shí)間偏差約為1ns,。因而探頭非常重要,,詳見本站"測(cè)試附件及連接探頭"。a,、探頭的阻性負(fù)載,,也就是探頭的接入系統(tǒng)中以后對(duì)系統(tǒng)電流的分流作用的小,在數(shù)字系統(tǒng)中,。河源PCIE分析儀品牌分析儀哪里買,?找歐奧!

歐奧電子是Prodigy在中國(guó)區(qū)的官方授權(quán)合作伙伴,,ProdigyMPHY,UniPro,UFS總線協(xié)議分析儀測(cè)試解決方案不會(huì)收到EAR進(jìn)出口方面的管制,。同時(shí)還有代理其他總類的協(xié)議分析儀,包括嵌入式設(shè)備用的SDIO協(xié)議分析儀,QSPI協(xié)議分析儀及訓(xùn)練器,I3C協(xié)議分析儀及訓(xùn)練器,RFFE協(xié)議分析儀及訓(xùn)練器等等,。我司還有代理SPMI協(xié)議分析儀及訓(xùn)練器,車載以太網(wǎng)分析儀,,以及各種相關(guān)的基于示波器的解碼軟件和SI測(cè)試軟件。同時(shí),,歐奧電子也有提供高難度焊接,,以及高速信號(hào),,如UFS,DDR3/DDR4,,USBtypeC等高速協(xié)議抓取和分析的服務(wù),。DampedResistorProbing),電阻匹配探測(cè)(ResistiveDividerProbing)。短線探測(cè)會(huì)增加電容負(fù)載,。舉例:探頭電容負(fù)載是,,連接短線是50歐姆微帶線。C=3pF/in),,長(zhǎng)度1英寸,。則整個(gè)探頭的電容負(fù)載是,這個(gè)短線是電容負(fù)載的主要部分,。被測(cè)系統(tǒng)可容忍的負(fù)載電容是多少呢,?需要參考被測(cè)電路的系統(tǒng)上升時(shí)間,一般規(guī)則:短線的電氣長(zhǎng)度<>PCB傳輸延遲:150ps/in系統(tǒng)上升時(shí)間:500ps則電氣長(zhǎng)度:則短線長(zhǎng)度:(100ps)/(150ps/in)=,。如果沒法減小短線長(zhǎng)度,,可以試著用阻尼電阻探測(cè)的方式。阻尼電阻有2個(gè)作用:隔離來自短線的電容,,消減來自短線的反射,。

定時(shí)分析與狀態(tài)分析的主要區(qū)別是:定時(shí)分析由內(nèi)部時(shí)鐘控制采樣,采樣與被測(cè)系統(tǒng)是異步的,;狀態(tài)分析由被測(cè)系統(tǒng)時(shí)鐘控制采樣,,采樣與被測(cè)系統(tǒng)是同步的。用定時(shí)分析查看事件“什么時(shí)候”發(fā)生,,用狀態(tài)分析檢查發(fā)生了“什么”事件,。定時(shí)分析通常用波形顯示數(shù)據(jù),狀態(tài)分析通常用列表顯示數(shù)據(jù),。六,、小結(jié)邏輯分析儀主要用來測(cè)試以微處理器為的數(shù)字系統(tǒng),在硬件電路,、嵌入式系統(tǒng)和監(jiān)控軟件的研制和調(diào)試過程中,,都是一個(gè)必備的工具。邏輯分析儀具有豐富的觸發(fā)條件,,不管被測(cè)系統(tǒng)多么復(fù)雜,,邏輯分析儀都能準(zhǔn)確地找到那些隱蔽的、偶然的特殊時(shí)刻,,然后把觸發(fā)條件發(fā)生前后,各信號(hào)的時(shí)序圖和數(shù)據(jù)流顯示出來。問題也就看清楚了,不需要再絞盡腦汁的推理和猜測(cè)了,。SMBus邏輯分析儀/協(xié)議訓(xùn)練器找歐奧!

定時(shí)分析與狀態(tài)分析的主要區(qū)別是:定時(shí)分析由內(nèi)部時(shí)鐘控制采樣,采樣與被測(cè)系統(tǒng)是異步的,;狀態(tài)分析由被測(cè)系統(tǒng)時(shí)鐘控制采樣,,采樣與被測(cè)系統(tǒng)是同步的,。用定時(shí)分析查看事件“什么時(shí)候”發(fā)生,用狀態(tài)分析檢查發(fā)生了“什么”事件,。定時(shí)分析通常用波形顯示數(shù)據(jù),,狀態(tài)分析通常用列表顯示數(shù)據(jù),。六、小結(jié)邏輯分析儀主要用來測(cè)試以微處理器為的數(shù)字系統(tǒng),,在硬件電路,、嵌入式系統(tǒng)和監(jiān)控軟件的研制和調(diào)試過程中,,都是一個(gè)必備的工具。邏輯分析儀具有豐富的觸發(fā)條件,,不管被測(cè)系統(tǒng)多么復(fù)雜,,邏輯分析儀都能準(zhǔn)確地找到那些隱蔽的,、偶然的特殊時(shí)刻,,然后把觸發(fā)條件發(fā)生前后,,各信號(hào)的時(shí)序圖和數(shù)據(jù)流顯示出來,。問題也就看清楚了,,不需要再絞盡腦汁的推理和猜測(cè)了。歐奧電子是Prodigy在中國(guó)區(qū)的官方授權(quán)合作伙伴,,ProdigyMPHY,UniPro,UFS總線協(xié)議分析儀測(cè)試解決方案不會(huì)收到EAR進(jìn)出口方面的管制,。同時(shí)還有代理其他總類的協(xié)議分析儀,包括嵌入式設(shè)備用的SDIO協(xié)議分析儀,QSPI協(xié)議分析儀及訓(xùn)練器,I3C協(xié)議分析儀及訓(xùn)練器,RFFE協(xié)議分析儀及訓(xùn)練器等等,。我司還有代理SPMI協(xié)議分析儀及訓(xùn)練器,車載以太網(wǎng)分析儀,,以及各種相關(guān)的基于示波器的解碼軟件和SI測(cè)試軟件,。同時(shí),。分析儀源頭工廠,,一手勁爆價(jià),就找歐奧,!嘉興RFFE分析儀廠家

邏輯分析儀廠家哪家強(qiáng),?歐奧強(qiáng)!揭陽(yáng)PCIE分析儀電話

我們會(huì)找到信號(hào)與上升的Vref值交叉的位置,。如果Vref升至足夠高,信號(hào)的頂部軌跡將通過Vref,,我們便會(huì)看到眼的頂端。再將Vref升高一點(diǎn)會(huì)導(dǎo)致Vcomp保持在Vlo,,表示信號(hào)不會(huì)升至該電之,,將Vref移至零以下會(huì)看到眼的下半部。eyescan/eyefinder顯示窗口會(huì)在每個(gè)信號(hào)的eyescan圖下方顯示eyefinder交疊部分,,以此顯示eyefinder與eyescan之間的這一關(guān)系,。通過在eyescan圖中將Vth水平線向上和向下移動(dòng),,可以獲得距離眼中心該偏移量位置處的eyefinder視圖。無論用戶界面中的閾值如何設(shè)置,,邏輯分析儀的差分輸入將始終應(yīng)用于接收器。這意味著可通過將電壓閾值手動(dòng)設(shè)置為非零值允許在差分對(duì)中使用公共模式電壓,。如果信號(hào)擺幅中心與地線差距于100mV,,eyescan將自動(dòng)執(zhí)行此操作,。邏輯分析儀的觸發(fā)設(shè)置邏輯分析儀觸發(fā)非常困難,,而且還需花費(fèi)量時(shí)間,。假設(shè)如果知道如何編程,,則應(yīng)該可以毫不費(fèi)力地設(shè)置邏輯分析儀觸發(fā),。然而,,這是不可能的,,因?yàn)樵S多概念對(duì)邏輯分析來說都是的,。本節(jié)的目的就是介紹這些主要概念及如何有效地使用它們,。傳送帶類比:我們可以將邏輯分析儀的內(nèi)存比作一條很長(zhǎng)的傳送帶,,而從被測(cè)設(shè)備(DUT)獲取的樣本就像是傳送帶上的箱子。新的箱子被放置在傳送帶一端,。揭陽(yáng)PCIE分析儀電話

- 惠州邏輯分析儀報(bào)價(jià) 2025-04-22

- 福州SD分析儀售價(jià) 2025-04-22

- 佛山SD分析儀報(bào)價(jià) 2025-04-22

- 云浮邏輯分析儀 2025-04-22

- 成都UFS分析儀那家好 2025-04-22

- 江門SDIO分析儀收費(fèi) 2025-04-22

- 汕尾邏輯分析儀 2025-04-22

- 武漢UART分析儀那家好 2025-04-22

- 徐州UART分析儀價(jià)格 2025-04-22

- 揭陽(yáng)邏輯分析儀那家好 2025-04-22

- 汕頭國(guó)產(chǎn)熱電偶私人定做 2025-04-22

- 上海thinklab超純水機(jī)批發(fā)定制 2025-04-22

- 金華薄型氣缸廠 2025-04-22

- 電力振動(dòng)監(jiān)測(cè)文獻(xiàn) 2025-04-22

- 寧波3D數(shù)碼顯微鏡測(cè)凹槽深寬比 2025-04-22

- 江西激光空氣粒子計(jì)數(shù)器制造商 2025-04-22

- 南京一類水超純水機(jī)銷售 2025-04-22

- 杭州分體式超聲波液位差計(jì)制造 2025-04-22

- 多級(jí)泵振動(dòng)分析儀公司 2025-04-22

- 廣東das光纖聲波傳感系統(tǒng) 2025-04-22