咸寧PCB制板價格大全

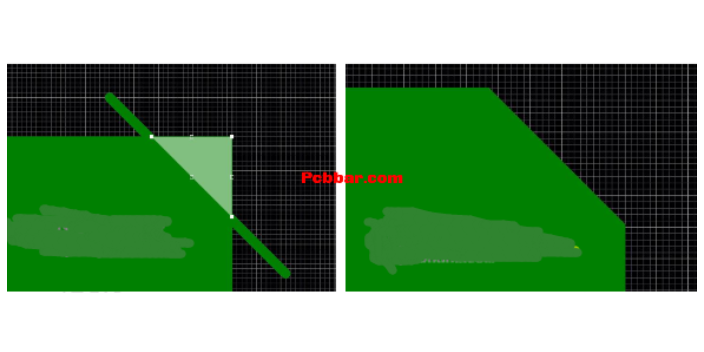

差分走線及等長注意事項1.阻抗匹配的情況下,,間距越小越好2.蛇狀線<圓弧轉(zhuǎn)角<45度轉(zhuǎn)角<90度轉(zhuǎn)角(等長危害程度)蛇狀線的危害比轉(zhuǎn)角小一些,,因此若空間許可,盡量用蛇狀線代替轉(zhuǎn)角,,來達(dá)成等長的目的,。3.圓弧轉(zhuǎn)角<45度轉(zhuǎn)角<90度轉(zhuǎn)角(走線轉(zhuǎn)角危害程度)轉(zhuǎn)角所造成的相位差,以90度轉(zhuǎn)角大,,45度轉(zhuǎn)角次之,,圓滑轉(zhuǎn)角小。圓滑轉(zhuǎn)角所產(chǎn)生的共模噪聲比90度轉(zhuǎn)角小,。4.等長優(yōu)先級大于間距間距<長度差分訊號不等長,,會造成邏輯判斷錯誤,,而間距不固定對邏輯判斷的影響,幾乎是微乎其微,。而阻抗方面,,間距不固定雖然會有變化,但其變化通常10%以內(nèi),,只相當(dāng)于一個過孔的影響,。至于EMI幅射干擾的增加,與抗干擾能力的下降,,可在間距變化之處,,用GNDFill技巧,,并多打過孔直接連到MainGND,,以減少EMI幅射干擾,以及被動干擾的機(jī)會[29-30],。如前述,,差分訊號重要的就是要等長,因此若無法兼顧固定間距與等長,,則需以等長為優(yōu)先考慮,。當(dāng)PCB制板兩面都有貼片時,按此規(guī)則標(biāo)記制板兩面,。咸寧PCB制板價格大全

SDRAM的PCB布局布線要求1,、對于數(shù)據(jù)信號,如果32bit位寬數(shù)據(jù)總線中的低16位數(shù)據(jù)信號掛接其它緩沖器的情況,,SDRAM作為接收器即寫進(jìn)程時,,首先要保證SDRAM接收端的信號完整性,將SDRAM芯片放置在信號鏈路的遠(yuǎn)端,,對于地址及控制信號的也應(yīng)該如此處理,。2、對于掛了多片SDRAM芯片和其它器件的情況,,從信號完整性角度來考慮,,SDRAM芯片集中緊湊布局。3,、源端匹配電阻應(yīng)靠近輸出管腳放置,,退耦電容靠近器件電源管腳放置。4,、SDRAM的數(shù)據(jù),、地址線推薦采用菊花鏈布線線和遠(yuǎn)端分支方式布線,Stub線頭短,。5,、對于SDRAM總線,,一般要對SDRAM的時鐘、數(shù)據(jù),、地址及控制信號在源端要串聯(lián)上33歐姆或47歐姆的電阻,;數(shù)據(jù)線串阻的位置可以通過SI仿真確定。6,、對于時鐘信號采用∏型(RCR)濾波,,走在內(nèi)層,保證3W間距,。7,、對于時鐘頻率在50MHz以下時一般在時序上沒有問題,走線短,。8,、對于時鐘頻率在100MHz以上數(shù)據(jù)線需要保證3W間距。9,、對于電源的處理,,SDRAM接口I/O供電電壓多是3.3V,首先要保證SDRAM器件每個電源管腳有一個退耦電容,,每個SDRAM芯片有一兩個大的儲能電容,,退耦電容要靠近電源管腳放置,儲能大電容要靠近SDRAM器件放置,,注意電容扇出方式,。10、SDRAM的設(shè)計案列宜昌正規(guī)PCB制板原理層壓是抑制PCB制板電磁干擾的重要手段,。

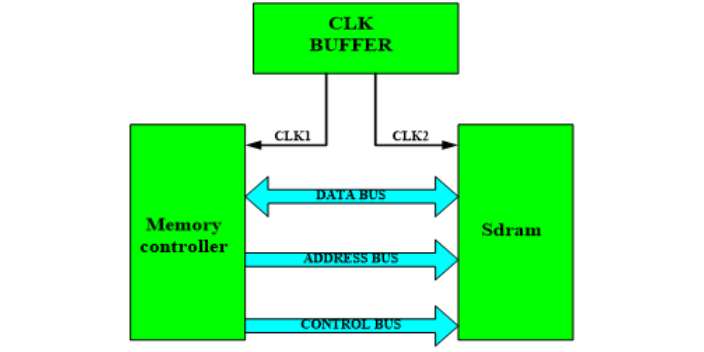

SDRAM時鐘源同步和外同步1,、源同步:是指時鐘與數(shù)據(jù)同時在兩個芯片之間間傳輸,不需要外部時鐘源來給SDRAM提供時鐘,,CLK由SDRAM控制芯片(如CPU)輸出,,數(shù)據(jù)總線、地址總線,、控制總線信號由CLK來觸發(fā)和鎖存,,CLK必須與數(shù)據(jù)總線、地址總線,、控制總線信號滿足一定的時序匹配關(guān)系才能保證SDRAM正常工作,,即CLK必須與數(shù)據(jù)總線、地址總線,、控制總線信號在PCB上滿足一定的傳輸線長度匹配,。2、外同步:由外部時鐘給系統(tǒng)提供參考時鐘,,數(shù)據(jù)從發(fā)送到接收需要兩個時鐘,,一個鎖存發(fā)送數(shù)據(jù),,一個鎖存接收數(shù)據(jù),在一個時鐘周期內(nèi)完成,,對于SDRAM及其控制芯片,,參考時鐘CLK1、CLK2由外部時鐘驅(qū)動產(chǎn)生,,此時CLK1,、CLK2到達(dá)SDRAM及其控制芯片的延時必須滿足數(shù)據(jù)總線、地址總線及控制總線信號的時序匹配要求,,即CLK1,、CLK2必須與數(shù)據(jù)總線、地址總線,、控制總線信號在PCB上滿足一定的傳輸線長度匹配,。

PCB制板設(shè)計中減少環(huán)路面積和感應(yīng)電流的另一種方法是減少互連器件之間的并聯(lián)路徑。當(dāng)需要使用大于30cm的信號連接線時,,可以使用保護(hù)線,。更好的方法是在信號線附近放置一個地層。信號線應(yīng)在距保護(hù)線或接地線層13mm以內(nèi),。每個敏感元件的長信號線(>30cm)或電源線與其接地線交叉。交叉線必須從上到下或從左到右按一定的間隔排列,。2.電路連接長度長的信號線也可以作為接收ESD脈沖能量的天線,,盡量使用較短的信號線可以降低信號線作為接收ESD電磁場的天線的效率。盡量將互連設(shè)備彼此相鄰放置,,以減少互連印刷線路的長度,。3.地面電荷注入ESD接地層的直接放電可能會損壞敏感電路。除TVS二極管外,,還應(yīng)使用一個或多個高頻旁路電容,,放置在易損元件的電源和地之間。旁路電容減少電荷注入,,并保持電源和接地端口之間的電壓差,。TVS分流感應(yīng)電流,保持TVS箝位電壓的電位差,。TVS和電容應(yīng)盡可能靠近受保護(hù)的IC,,TVS到地的通道和電容的引腳長度應(yīng)比較短,以降低寄生電感效應(yīng),。PCB制板設(shè)計是與性能相關(guān)的階段,。

常用的拓?fù)浣Y(jié)構(gòu)常用的拓?fù)浣Y(jié)構(gòu)包括點對點、菊花鏈,、遠(yuǎn)端簇型,、星型等,。1、點對點拓?fù)鋚oint-to-pointscheduling:該拓?fù)浣Y(jié)構(gòu)簡單,,整個網(wǎng)絡(luò)的阻抗特性容易控制,,時序關(guān)系也容易控制,常見于高速雙向傳輸信號線,。2,、菊花鏈結(jié)構(gòu)daisy-chainscheduling:菊花鏈結(jié)構(gòu)也比較簡單,阻抗也比較容易控制,。3,、fly-byscheduling:該結(jié)構(gòu)是特殊的菊花鏈結(jié)構(gòu),stub線為0的菊花鏈,。不同于DDR2的T型分支拓?fù)浣Y(jié)構(gòu),,DDR3采用了fly-by拓?fù)浣Y(jié)構(gòu),以更高的速度提供更好的信號完整性,。fly-by信號是命令,、地址,控制和時鐘信號,。4,、星形結(jié)構(gòu)starscheduling:該結(jié)構(gòu)布線比較復(fù)雜,阻抗不容易控制,,但是由于星形堆成,,所以時序比較容易控制。5,、遠(yuǎn)端簇結(jié)構(gòu)far-endclusterscheduling:遠(yuǎn)端簇結(jié)構(gòu)可以算是星形結(jié)構(gòu)的變種,,要求是D到中心點的長度要遠(yuǎn)遠(yuǎn)長于各個R到中心連接點的長度。各個R到中心連接點的距離要盡量等長,,匹配電阻放置在D附近,,常用語DDR的地址、數(shù)據(jù)線的拓?fù)浣Y(jié)構(gòu),。在實際的PCB設(shè)計過程中,,對于關(guān)鍵信號,應(yīng)通過信號完整性分析來決定采用哪一種拓?fù)浣Y(jié)構(gòu),。什么叫作PCB制板打樣,?武漢打造PCB制板價格大全

根據(jù)電路規(guī)模設(shè)置多層次PCB制板。咸寧PCB制板價格大全

HDI主板主要分為一階,、二階,、三階、Anylayer HDI,,特征尺寸逐漸縮小,,制造難度也逐漸增加,。目前在電子終端產(chǎn)品上應(yīng)用比較多的是三階、四階或AnylayerHDI主板,。AnylayerHDI被稱為任意階或任意層HDI主板,,也有稱作ELIC(Every Layer Interconnect)HDI。目前在電子終端產(chǎn)品上應(yīng)用比較多的Anylayer是10層或12層,。蘋果手機(jī)主板從iPhone4S導(dǎo)入使用Anylayer HDI,,而華為目前的旗艦全系列主要使用為Anylayer HDI,例如華為P30系列主板分為MainPCB和RF PCB,,都采用Anylayer HDI,,Mate20和Mate30系列也是采用Anylayer HDI主板。咸寧PCB制板價格大全

- 深圳常規(guī)PCB培訓(xùn)規(guī)范 2025-06-02

- 印制PCB制版多少錢 2025-06-02

- 湖北如何PCB培訓(xùn)廠家 2025-06-02

- 黃岡焊接PCB制版布線 2025-06-02

- 荊門常規(guī)PCB設(shè)計布線 2025-06-02

- 荊門焊接PCB制版原理 2025-06-02

- 打造PCB制版 2025-06-02

- 鄂州哪里的PCB設(shè)計加工 2025-06-02

- 專業(yè)PCB培訓(xùn)包括哪些 2025-06-02

- 荊州正規(guī)PCB制版布線 2025-06-02

- 福建311光纜性能 2025-06-02

- 杭州JVC攝像機(jī)光纜阻燃 2025-06-02

- 貴州鋰電池化成銷售價格 2025-06-02

- 遼寧進(jìn)口干式真空有載分接開關(guān) 2025-06-02

- 浙江厚膜光刻膠價格 2025-06-02

- 溫州磁懸浮傳輸線安裝 2025-06-02

- 中山全自動雕刻直流電機(jī)批發(fā)零售 2025-06-02

- 低壓車燈電子線 2025-06-02

- 智能化新能源線束售后服務(wù) 2025-06-02

- 惠州防靜電有機(jī)玻璃板 2025-06-02