-

惟精環(huán)境藻類智能分析監(jiān)測系統(tǒng),為水源安全貢獻(xiàn)科技力量,!

-

快來擁抱無線遠(yuǎn)程打印新時(shí)代,,惟精智印云盒、讓打印變得如此簡單

-

攜手共進(jìn),,惟精環(huán)境共探環(huán)保行業(yè)發(fā)展新路徑

-

惟精環(huán)境:科技賦能,,守護(hù)綠水青山

-

南京市南陽商會(huì)新春聯(lián)會(huì)成功召開

-

惟精環(huán)境順利通過“江蘇省民營科技企業(yè)”復(fù)評(píng)復(fù)審

-

“自動(dòng)?化監(jiān)測技術(shù)在水質(zhì)檢測中的實(shí)施與應(yīng)用”在《科學(xué)家》發(fā)表

-

熱烈祝賀武漢市概念驗(yàn)證中心(武漢科技大學(xué))南京分中心掛牌成立

-

解鎖流域水質(zhì)密碼,“三維熒光水質(zhì)指紋”鎖定排污嫌疑人,!

-

重磅政策,,重點(diǎn)流域水環(huán)境綜合治理資金支持可達(dá)總投資的80%

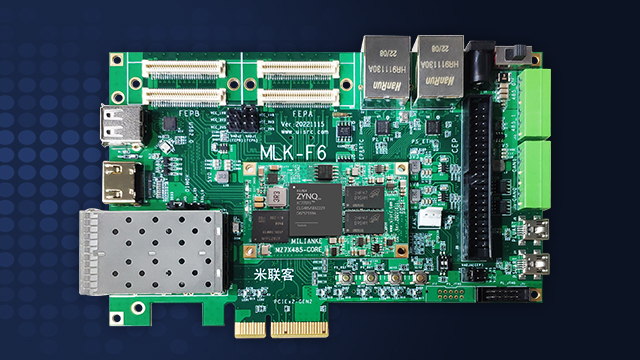

天津賽靈思FPGA開發(fā)板平臺(tái)

FPGA 開發(fā)板在機(jī)器人領(lǐng)域發(fā)揮著作用,助力機(jī)器人實(shí)現(xiàn)更加智能的動(dòng)作,。在工業(yè)機(jī)器人中,,開發(fā)板用于處理機(jī)器人運(yùn)動(dòng)算法,根據(jù)預(yù)設(shè)的路徑和任務(wù)要求,,精確機(jī)器人各個(gè)關(guān)節(jié)的運(yùn)動(dòng),。通過與電機(jī)驅(qū)動(dòng)器通信,,開發(fā)板向電機(jī)發(fā)送信號(hào),實(shí)現(xiàn)對(duì)電機(jī)轉(zhuǎn)速,、轉(zhuǎn)矩和位置的精確調(diào)節(jié),,從而保證機(jī)器人能夠準(zhǔn)確地完成各種復(fù)雜的操作,如搬運(yùn),、裝配,、焊接等任務(wù)。在服務(wù)機(jī)器人中,,開發(fā)板除了負(fù)責(zé)運(yùn)動(dòng)外,,還承擔(dān)著人機(jī)交互和環(huán)境感知數(shù)據(jù)處理的任務(wù)。開發(fā)板接收來自攝像頭,、麥克風(fēng),、超聲波傳感器等設(shè)備采集的環(huán)境信息,通過算法對(duì)這些信息進(jìn)行分析和理解,,使機(jī)器人能夠感知周圍環(huán)境,,與人類進(jìn)行自然交互。例如,,服務(wù)機(jī)器人在遇到障礙物時(shí),,開發(fā)板根據(jù)傳感器數(shù)據(jù)及時(shí)調(diào)整機(jī)器人的運(yùn)動(dòng)方向,避免碰撞,;在與用戶交流時(shí),,開發(fā)板對(duì)語音信號(hào)進(jìn)行處理和識(shí)別,理解用戶的指令并做出相應(yīng)的回應(yīng),,提升機(jī)器人的智能化水平和服務(wù)質(zhì)量,。虛擬現(xiàn)實(shí)設(shè)備中,F(xiàn)PGA 開發(fā)板保障畫面流暢與交互體驗(yàn),。天津賽靈思FPGA開發(fā)板平臺(tái)

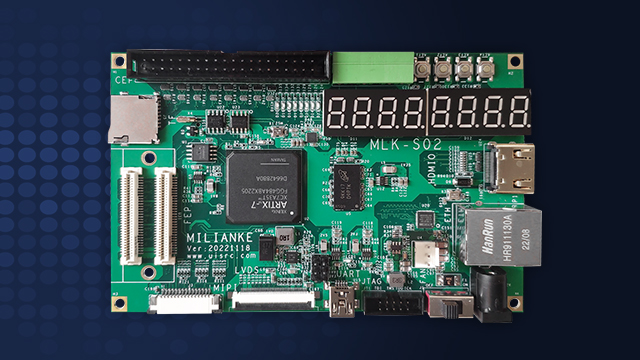

FPGA開發(fā)板在教育教學(xué)中具有重要的價(jià)值,。對(duì)于高校電子信息類的學(xué)生而言,開發(fā)板是將理論知識(shí)轉(zhuǎn)化為實(shí)踐能力的重要媒介,。在數(shù)字電路課程學(xué)習(xí)中,,學(xué)生通過在開發(fā)板上實(shí)現(xiàn)簡單的邏輯電路,如計(jì)數(shù)器,、譯碼器等,,直觀地理解數(shù)字電路的工作原理與設(shè)計(jì)方法。在學(xué)習(xí)硬件描述語言時(shí),,學(xué)生利用開發(fā)板進(jìn)行實(shí)際項(xiàng)目練習(xí),,從簡單的LED閃爍到復(fù)雜的數(shù)碼管動(dòng)態(tài)顯示,逐步掌握Verilog或VHDL語言的編程技巧,。在綜合性課程設(shè)計(jì)與畢業(yè)設(shè)計(jì)中,,開發(fā)板更是學(xué)生展示創(chuàng)新能力的平臺(tái),。學(xué)生可以基于開發(fā)板開展如智能小車設(shè)計(jì)、簡易數(shù)字示波器制作等項(xiàng)目,,綜合運(yùn)用多門課程所學(xué)知識(shí),,鍛煉系統(tǒng)設(shè)計(jì),、調(diào)試與優(yōu)化的能力,,培養(yǎng)學(xué)生的工程實(shí)踐素養(yǎng)與創(chuàng)新思維,為未來從事電子信息相關(guān)行業(yè)的工作奠定堅(jiān)實(shí)的基礎(chǔ),。 湖南賽靈思FPGA開發(fā)板交流創(chuàng)新教育課程里,,F(xiàn)PGA 開發(fā)板培養(yǎng)學(xué)生的實(shí)踐與創(chuàng)新能力。

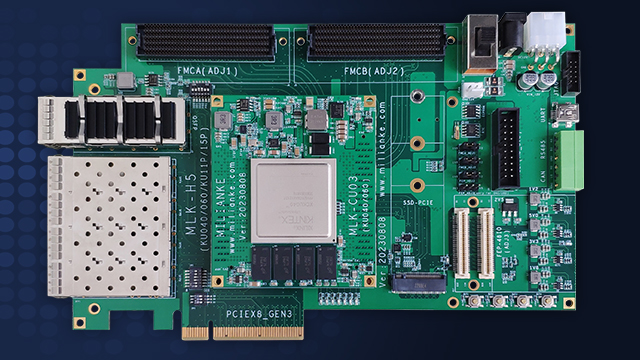

FPGA開發(fā)板在視頻監(jiān)控系統(tǒng)中的應(yīng)用極大地提升了監(jiān)控的智能化水平,。開發(fā)板可以對(duì)多路攝像頭采集的視頻流進(jìn)行實(shí)時(shí)處理,。在視頻壓縮方面,實(shí)現(xiàn)的視頻編碼算法,,如,,將視頻數(shù)據(jù)壓縮后進(jìn)行存儲(chǔ)與傳輸,減少存儲(chǔ)空間與網(wǎng)絡(luò)帶寬的占用,。在視頻分析環(huán)節(jié),,通過在FPGA上運(yùn)行目標(biāo)檢測算法,能夠自動(dòng)識(shí)別視頻中的人員,、車輛等目標(biāo)物體,,并對(duì)其行為進(jìn)行分析。例如,,判斷人員是否有異常行為,,如徘徊、奔跑等,;檢測車輛是否違規(guī)行駛,,如超速、逆行等,。一旦發(fā)現(xiàn)異常情況,,開發(fā)板可立即觸發(fā)報(bào)警機(jī)制,通知監(jiān)控人員進(jìn)行處理,。此外,,開發(fā)板還可以實(shí)現(xiàn)視頻拼接功能,將多個(gè)攝像頭的畫面拼接成一個(gè)全景畫面,,提供更廣闊的監(jiān)控視野,,為安防監(jiān)控領(lǐng)域提供強(qiáng)大的技術(shù)支持,公共安全與社會(huì)穩(wěn)定,。

FPGA開發(fā)板在汽車電子領(lǐng)域的應(yīng)用不斷拓展,,為汽車的智能化與信息化發(fā)展提供支持,。在車載系統(tǒng)中,開發(fā)板可用于實(shí)現(xiàn)高清視頻播放,、音頻處理以及多媒體交互功能,。通過HDMI接口連接車載顯示屏,實(shí)現(xiàn)高清視頻的流暢播放,;利用音頻處理模塊,,為用戶提供質(zhì)量的音頻體驗(yàn)。同時(shí),,開發(fā)板還可以與車載網(wǎng)絡(luò)系統(tǒng)進(jìn)行通信,,獲取車輛的相關(guān)信息,如車速,、油耗等,,并在系統(tǒng)界面上進(jìn)行顯示,方便用戶了解車輛狀態(tài),。在自動(dòng)駕駛輔助系統(tǒng)中,,開發(fā)板負(fù)責(zé)處理來自攝像頭、雷達(dá)等傳感器的數(shù)據(jù),。對(duì)攝像頭采集的圖像進(jìn)行識(shí)別與分析,,檢測道路、車輛,、行人等目標(biāo),;對(duì)雷達(dá)數(shù)據(jù)進(jìn)行處理,計(jì)算目標(biāo)物體的距離與速度,?;谶@些數(shù)據(jù),在FPGA上實(shí)現(xiàn)相應(yīng)的算法,,為駕駛員提供駕駛輔助信息,,如自動(dòng)緊急制動(dòng)預(yù)警、車道偏離提醒等,,提高駕駛的安全性與舒適性,,推動(dòng)汽車電子技術(shù)的不斷進(jìn)步。 FPGA 開發(fā)板預(yù)留拓展接口,,方便開發(fā)者添加功能模塊升級(jí)系統(tǒng),。

FPGA 開發(fā)板的開源社區(qū)為開發(fā)者提供了豐富的資源與交流平臺(tái)。眾多開發(fā)者在開源社區(qū)分享基于開發(fā)板的設(shè)計(jì)項(xiàng)目,,涵蓋從基礎(chǔ)的 LED 閃爍,、數(shù)碼管顯示,到復(fù)雜的圖像處理,、通信協(xié)議實(shí)現(xiàn)等各類案例,。這些開源項(xiàng)目不僅包含完整的代碼,,還附有詳細(xì)的設(shè)計(jì)文檔與說明,開發(fā)者可從中學(xué)習(xí)新的技術(shù)與開發(fā)思路,。同時(shí),,開發(fā)者也可將自己的項(xiàng)目成果分享到社區(qū),與其他開發(fā)者交流合作,,共同解決開發(fā)過程中遇到的問題,。開源社區(qū)的存在促進(jìn)了技術(shù)的共享與創(chuàng)新,降低了開發(fā)門檻,,讓更多開發(fā)者能夠參與到 FPGA 技術(shù)的研究與應(yīng)用中,,推動(dòng) FPGA 開發(fā)板在各個(gè)領(lǐng)域的廣泛應(yīng)用,。預(yù)算有限時(shí),,優(yōu)先挑選具備豐富教程、價(jià)格親民的經(jīng)典入門級(jí) FPGA 開發(fā)板較為合適,。廣東入門級(jí)FPGA開發(fā)板設(shè)計(jì)

航空航天研究中,,F(xiàn)PGA 開發(fā)板保障信號(hào)處理與數(shù)據(jù)傳輸?shù)目煽啃浴L旖蛸愳`思FPGA開發(fā)板平臺(tái)

基于FPGA開發(fā)板進(jìn)行項(xiàng)目開發(fā)時(shí),,軟件工具鏈起著關(guān)鍵作用,。以Altera(現(xiàn)Intel)的QuartusPrime軟件為例,其提供了完整的FPGA開發(fā)流程支持,。在設(shè)計(jì)輸入階段,,開發(fā)者既可以使用硬件描述語言Verilog或VHDL編寫代碼,描述電路的邏輯功能,;也可以采用原理圖輸入方式,,通過圖形化的方式搭建電路模塊,直觀展示設(shè)計(jì)架構(gòu),。完成設(shè)計(jì)輸入后,,QuartusPrime的綜合功能會(huì)將代碼或原理圖轉(zhuǎn)換為門級(jí)網(wǎng)表,針對(duì)目標(biāo)FPGA芯片的邏輯資源進(jìn)行優(yōu)化映射,。接著是布局布線環(huán)節(jié),,軟件根據(jù)芯片的物理結(jié)構(gòu),合理安排邏輯單元的位置,,并完成各單元之間的連線,,確保信號(hào)傳輸?shù)臏?zhǔn)確性與穩(wěn)定性。通過編程下載功能,,將生成的配置文件燒錄到FPGA開發(fā)板中,,使設(shè)計(jì)在硬件上得以實(shí)現(xiàn)。同時(shí),,該軟件還提供了仿真功能,,方便開發(fā)者在硬件實(shí)現(xiàn)前對(duì)設(shè)計(jì)進(jìn)行功能驗(yàn)證,,減少開發(fā)過程中的錯(cuò)誤與風(fēng)險(xiǎn)。 天津賽靈思FPGA開發(fā)板平臺(tái)

- 天津開發(fā)板FPGA開發(fā)板特點(diǎn)與應(yīng)用 2025-06-19

- 福建FPGA定制項(xiàng)目教學(xué) 2025-06-19

- 進(jìn)口FPGA定制項(xiàng)目學(xué)習(xí)視頻 2025-06-19

- 中國臺(tái)灣工控板FPGA開發(fā)板教學(xué) 2025-06-19

- 江西學(xué)習(xí)FPGA開發(fā)板特點(diǎn)與應(yīng)用 2025-06-19

- 福建工控板FPGA開發(fā)板工業(yè)模板 2025-06-19

- 廣東開發(fā)FPGA開發(fā)板論壇 2025-06-19

- 山東MPSOCFPGA開發(fā)板代碼 2025-06-19

- 湖北國產(chǎn)FPGA開發(fā)板代碼 2025-06-19

- 定制FPGA定制項(xiàng)目教學(xué) 2025-06-19

- 崇明區(qū)標(biāo)準(zhǔn)LTE模塊廠家現(xiàn)貨 2025-06-19

- 廣東醫(yī)療PCB供應(yīng)商 2025-06-19

- 北京消費(fèi)TVS瞬變抑制二極管報(bào)價(jià) 2025-06-19

- 常州本地汽車連接器 2025-06-19

- 福建B5819W二極管OEM 2025-06-19

- 汽車傳感器防水透氣帽原廠 2025-06-19

- 湖北貼片電感3a 2025-06-19

- 常州壓板鍍銀線在線詢價(jià) 2025-06-19

- 佛山普通二極管廠家 2025-06-19

- 廣西廣播系統(tǒng)哪個(gè)牌子好 2025-06-19