-

520的甜蜜承諾,,專(zhuān)菱觀光車(chē)以整車(chē)焊接守護(hù)您的安全之旅

-

旅游日,,專(zhuān)菱觀光車(chē)為旅游業(yè)注入新動(dòng)力

-

專(zhuān)菱:觀光車(chē)上安裝雨簾,很有必要,!

-

景區(qū)老板都在問(wèn),,這款觀光車(chē)憑什么可以省電50%,?

-

用了這款電動(dòng)觀光車(chē),游客滿(mǎn)意度直接飆升!「專(zhuān)菱」

-

南岳旅游觀光車(chē):暢行景區(qū)的便捷之選「專(zhuān)菱」

-

專(zhuān)菱:如何判斷觀光車(chē)電池是否需要更換,?

-

探索觀光車(chē)駕駛的藝術(shù):解鎖理論考核的密鑰「專(zhuān)菱」

-

天氣轉(zhuǎn)冷,,電動(dòng)觀光車(chē)該如何保養(yǎng)「專(zhuān)菱」

-

專(zhuān)菱:觀光車(chē)裝上雨簾,很有必要,!

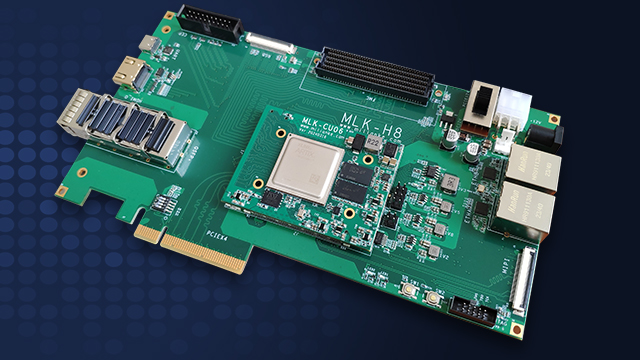

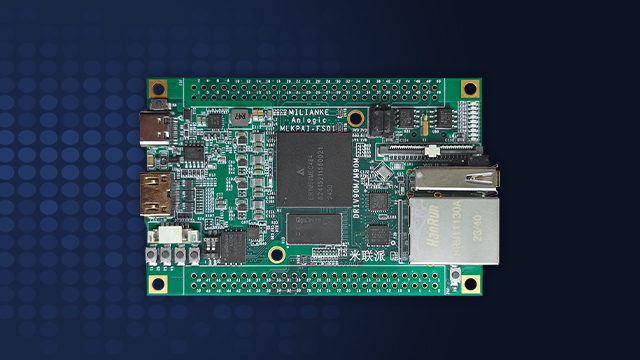

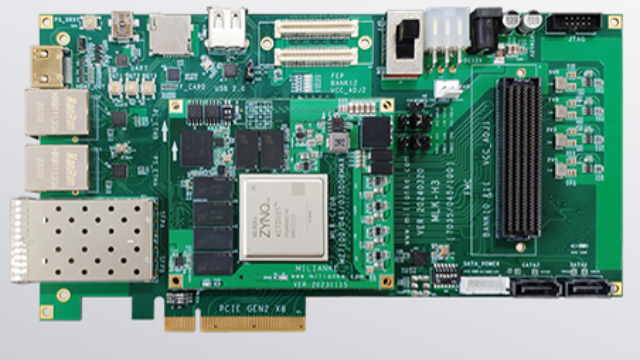

廣東入門(mén)級(jí)FPGA開(kāi)發(fā)板模塊

隨著人工智能技術(shù)發(fā)展,,F(xiàn)PGA 開(kāi)發(fā)板與人工智能的結(jié)合成為新的研究方向。開(kāi)發(fā)板可實(shí)現(xiàn)人工智能算法的硬件加速,,提高算法執(zhí)行效率,。在邊緣計(jì)算場(chǎng)景中,F(xiàn)PGA 開(kāi)發(fā)板部署在靠近數(shù)據(jù)源位置,,對(duì)數(shù)據(jù)進(jìn)行實(shí)時(shí)處理與分析,,減少數(shù)據(jù)傳輸延遲,保護(hù)數(shù)據(jù)隱私,。例如,,在智能安防監(jiān)控中,開(kāi)發(fā)板利用人工智能算法對(duì)視頻流進(jìn)行分析,,實(shí)現(xiàn)目標(biāo)識(shí)別,、行為分析等功能,為安防領(lǐng)域提供更智能,、高效解決方案,。這種結(jié)合推動(dòng)人工智能技術(shù)在實(shí)際應(yīng)用中的落地與發(fā)展,拓展 FPGA 開(kāi)發(fā)板的應(yīng)用領(lǐng)域,。金融科技應(yīng)用時(shí),,F(xiàn)PGA 開(kāi)發(fā)板加速數(shù)據(jù)處理與交易決策。廣東入門(mén)級(jí)FPGA開(kāi)發(fā)板模塊

FPGA 開(kāi)發(fā)板的升級(jí)與拓展能力為其應(yīng)用帶來(lái)更多可能性,。隨著技術(shù)發(fā)展,,開(kāi)發(fā)者可通過(guò)更新 FPGA 的配置文件,為開(kāi)發(fā)板添加新功能或優(yōu)化現(xiàn)有功能,。許多開(kāi)發(fā)板預(yù)留拓展接口,,開(kāi)發(fā)者可根據(jù)項(xiàng)目需求添加額外功能模塊。如在圖像識(shí)別項(xiàng)目中,,添加攝像頭模塊獲取圖像數(shù)據(jù),;在定位導(dǎo)航項(xiàng)目中,接入 GPS 模塊獲取位置信息,。這種升級(jí)與拓展能力使 FPGA 開(kāi)發(fā)板能夠適應(yīng)不斷變化的應(yīng)用需求,,延長(zhǎng)開(kāi)發(fā)板的使用壽命,提高其性?xún)r(jià)比,,在不同項(xiàng)目與應(yīng)用場(chǎng)景中持續(xù)發(fā)揮重要作用,,滿(mǎn)足開(kāi)發(fā)者多樣化的開(kāi)發(fā)需求,。遼寧開(kāi)發(fā)FPGA開(kāi)發(fā)板代碼FPGA 開(kāi)發(fā)板的硬件與軟件協(xié)同設(shè)計(jì),確保系統(tǒng)穩(wěn)定運(yùn)行,。

FPGA開(kāi)發(fā)板作為數(shù)字電路設(shè)計(jì)與驗(yàn)證的重要載體,,其硬件架構(gòu)設(shè)計(jì)融合了多種關(guān)鍵組件。開(kāi)發(fā)板上的FPGA芯片是實(shí)現(xiàn)邏輯功能的器件,,不同型號(hào)的FPGA芯片在邏輯單元數(shù)量,、存儲(chǔ)資源、接口類(lèi)型等方面存在差異,。以常見(jiàn)的入門(mén)級(jí)開(kāi)發(fā)板為例,,往往搭載中低端FPGA芯片,能夠滿(mǎn)足初學(xué)者對(duì)基礎(chǔ)數(shù)字電路設(shè)計(jì)的實(shí)踐需求,。除了FPGA芯片,,開(kāi)發(fā)板還配備電源管理模塊,該模塊通過(guò)多級(jí)電壓轉(zhuǎn)換,,為FPGA芯片及其他外設(shè)提供穩(wěn)定且適配的供電電壓,。例如,將外部輸入的5V電壓轉(zhuǎn)換為FPGA芯片所需的,、等工作電壓,。此外,復(fù)位電路的存在確保開(kāi)發(fā)板在啟動(dòng)或異常情況下能恢復(fù)到預(yù)設(shè)狀態(tài),,晶振電路則為整個(gè)系統(tǒng)提供精細(xì)的時(shí)鐘信號(hào),這些硬件組件協(xié)同工作,,構(gòu)成了FPGA開(kāi)發(fā)板穩(wěn)定運(yùn)行的基礎(chǔ),。

FPGA開(kāi)發(fā)板在虛擬現(xiàn)實(shí)(VR)和增強(qiáng)現(xiàn)實(shí)(AR)領(lǐng)域有著重要的應(yīng)用價(jià)值,為用戶(hù)帶來(lái)更加沉浸式的體驗(yàn),。在VR設(shè)備中,,開(kāi)發(fā)板用于處理大量的圖形數(shù)據(jù)和傳感器數(shù)據(jù)。VR設(shè)備需要實(shí)時(shí)渲染出逼真的虛擬場(chǎng)景,,并根據(jù)用戶(hù)頭部的運(yùn)動(dòng)及時(shí)調(diào)整畫(huà)面視角,,這對(duì)數(shù)據(jù)處理速度和實(shí)時(shí)性要求極高。FPGA開(kāi)發(fā)板憑借其高速并行處理能力,,能夠?qū)D形數(shù)據(jù)進(jìn)行渲染和優(yōu)化,,確保虛擬場(chǎng)景的流暢顯示。同時(shí),,開(kāi)發(fā)板實(shí)時(shí)采集陀螺儀,、加速度計(jì)等傳感器的數(shù)據(jù),準(zhǔn)確用戶(hù)頭部的運(yùn)動(dòng)姿態(tài),,實(shí)現(xiàn)畫(huà)面的實(shí)時(shí)同步更新,,為用戶(hù)提供身臨其境的虛擬現(xiàn)實(shí)體驗(yàn)。在AR設(shè)備中,開(kāi)發(fā)板同樣發(fā)揮著關(guān)鍵作用,,對(duì)攝像頭采集的現(xiàn)實(shí)場(chǎng)景圖像和虛擬信息進(jìn)行融合處理,,使虛擬物體能夠真實(shí)地呈現(xiàn)在現(xiàn)實(shí)環(huán)境中,并且能夠隨著用戶(hù)的移動(dòng)和視角變化而實(shí)時(shí)調(diào)整,,增強(qiáng)現(xiàn)實(shí)與虛擬之間的交互性和沉浸感,,推動(dòng)VR和AR技術(shù)在教育、工業(yè)設(shè)計(jì)等領(lǐng)域的廣泛應(yīng)用,。 FPGA 開(kāi)發(fā)板的低功耗設(shè)計(jì),,適用于便攜式設(shè)備與電池供電場(chǎng)景。

FPGA開(kāi)發(fā)板在智能家居系統(tǒng)的集成中扮演著重要角色,。開(kāi)發(fā)板作為智能家居系統(tǒng)單元,,通過(guò)多種通信方式連接家中的各類(lèi)智能設(shè)備。利用ZigBee,、Z-Wave等低功耗無(wú)線通信協(xié)議,,與智能插座、智能門(mén)鎖,、智能窗簾等設(shè)備進(jìn)行通信,,實(shí)現(xiàn)對(duì)這些設(shè)備的遠(yuǎn)程狀態(tài)監(jiān)測(cè)。例如,,用戶(hù)可以通過(guò)手機(jī)APP遠(yuǎn)程智能插座的開(kāi)關(guān),,電器設(shè)備的通電與斷電;查看智能門(mén)鎖的記錄,,了解家庭成員的出入情況,。開(kāi)發(fā)板還可以與智能音箱等語(yǔ)音交互設(shè)備進(jìn)行連接,實(shí)現(xiàn)語(yǔ)音功能,。用戶(hù)只需通過(guò)語(yǔ)音指令家中的智能設(shè)備,,如“打開(kāi)客廳燈光”“關(guān)閉空調(diào)”等,為用戶(hù)帶來(lái)便捷,、舒適的智能家居生活體驗(yàn),,提升家居生活的品質(zhì)與智能化程度。 科研實(shí)驗(yàn)時(shí),,F(xiàn)PGA 開(kāi)發(fā)板為新技術(shù)驗(yàn)證與算法測(cè)試提供可靠硬件平臺(tái),。上海開(kāi)發(fā)FPGA開(kāi)發(fā)板語(yǔ)法

視頻處理項(xiàng)目里,F(xiàn)PGA 開(kāi)發(fā)板實(shí)現(xiàn)高清視頻的實(shí)時(shí)編碼與解碼,。廣東入門(mén)級(jí)FPGA開(kāi)發(fā)板模塊

FPGA 開(kāi)發(fā)板的功耗管理是開(kāi)發(fā)者需要關(guān)注的重要方面,。在便攜式設(shè)備或電池供電的應(yīng)用場(chǎng)景中,降低開(kāi)發(fā)板功耗尤為關(guān)鍵,。開(kāi)發(fā)者可通過(guò)優(yōu)化 FPGA 邏輯設(shè)計(jì),,減少不必要的邏輯翻轉(zhuǎn),,降低芯片動(dòng)態(tài)功耗。合理配置開(kāi)發(fā)板外設(shè),,在不使用時(shí)將其設(shè)置為低功耗模式,,進(jìn)一步降低系統(tǒng)功耗。部分開(kāi)發(fā)板提供專(zhuān)門(mén)的功耗管理模塊,,幫助開(kāi)發(fā)者監(jiān)控與調(diào)節(jié)功耗,,通過(guò)軟件設(shè)置實(shí)現(xiàn)不同的功耗管理策略。良好的功耗管理使 FPGA 開(kāi)發(fā)板能夠在低功耗狀態(tài)下穩(wěn)定運(yùn)行,,滿(mǎn)足特定應(yīng)用場(chǎng)景對(duì)功耗的嚴(yán)格要求,,延長(zhǎng)設(shè)備續(xù)航時(shí)間。廣東入門(mén)級(jí)FPGA開(kāi)發(fā)板模塊

- 陜西學(xué)習(xí)FPGA開(kāi)發(fā)板學(xué)習(xí)板 2025-06-24

- 定制FPGA定制項(xiàng)目學(xué)習(xí)視頻 2025-06-24

- 湖北了解FPGA開(kāi)發(fā)板特點(diǎn)與應(yīng)用 2025-06-24

- 廣東使用FPGA開(kāi)發(fā)板資料下載 2025-06-24

- 河南開(kāi)發(fā)板FPGA開(kāi)發(fā)板資料下載 2025-06-24

- 上海嵌入式FPGA開(kāi)發(fā)板交流 2025-06-23

- 安徽國(guó)產(chǎn)FPGA開(kāi)發(fā)板套件 2025-06-23

- 陜西了解FPGA開(kāi)發(fā)板入門(mén) 2025-06-23

- 福建ZYNQFPGA開(kāi)發(fā)板工業(yè)模板 2025-06-23

- 四川工控板FPGA開(kāi)發(fā)板套件 2025-06-23

- 化學(xué)蝕刻機(jī)公司 2025-06-24

- 福建57(CN)連接器廠家供應(yīng) 2025-06-24

- 寧夏發(fā)光二極管銷(xiāo)售代理 2025-06-24

- 楊浦區(qū)進(jìn)口配電開(kāi)關(guān)報(bào)價(jià) 2025-06-24

- 高淳區(qū)哪里有集成電路芯片 2025-06-24

- 633 nm激光器費(fèi)用 2025-06-24

- 蘇州電動(dòng)叉車(chē)線束供應(yīng)商 2025-06-24

- 河北攝像頭開(kāi)發(fā)硬件開(kāi)發(fā)費(fèi)用是多少 2025-06-24

- 原廠原裝FDM32RV0049E-PQ64 2025-06-24

- 江蘇國(guó)產(chǎn)ESD二極管廠家 2025-06-24