山東開發(fā)板FPGA開發(fā)板設計

FPGA 開發(fā)板的功耗管理是開發(fā)者需要關注的重要方面,。在便攜式設備或電池供電的應用場景中,降低開發(fā)板功耗尤為關鍵,。開發(fā)者可通過優(yōu)化 FPGA 邏輯設計,,減少不必要的邏輯翻轉,降低芯片動態(tài)功耗,。合理配置開發(fā)板外設,,在不使用時將其設置為低功耗模式,進一步降低系統(tǒng)功耗,。部分開發(fā)板提供專門的功耗管理模塊,,幫助開發(fā)者監(jiān)控與調(diào)節(jié)功耗,通過軟件設置實現(xiàn)不同的功耗管理策略,。良好的功耗管理使 FPGA 開發(fā)板能夠在低功耗狀態(tài)下穩(wěn)定運行,,滿足特定應用場景對功耗的嚴格要求,延長設備續(xù)航時間,。金融科技應用時,,F(xiàn)PGA 開發(fā)板加速數(shù)據(jù)處理與交易決策。山東開發(fā)板FPGA開發(fā)板設計

FPGA開發(fā)板的開源社區(qū)為開發(fā)者提供了豐富的學習資源和創(chuàng)新靈感,。眾多開發(fā)者在開源社區(qū)分享自己基于開發(fā)板的設計項目,,涵蓋了從基礎應用到前沿技術的各個領域。這些開源項目不僅包含完整的代碼,,還附有詳細的設計文檔和說明,,開發(fā)者可以從中學習到不同的設計思路和技術實現(xiàn)方法。例如,,在學習數(shù)字信號處理算法在FPGA上的實現(xiàn)時,,開發(fā)者可以參考開源社區(qū)中的相關項目,了解如何利用FPGA的并行處理特性提高算法的執(zhí)行效率,。同時,,開發(fā)者也可以將自己的項目成果分享到社區(qū),與其他開發(fā)者進行交流和合作,,共同解決開發(fā)過程中遇到的問題,,這種技術共享和交流的氛圍促進了FPGA技術的發(fā)展和創(chuàng)新,讓更多的開發(fā)者能夠受益于開源社區(qū)的資源,。 黑龍江入門級FPGA開發(fā)板工程師FPGA 開發(fā)板豐富的存儲資源,,為數(shù)據(jù)處理提供有力支撐。

FPGA 開發(fā)板的硬件調(diào)試工具是開發(fā)者定位與解決問題的重要幫手,。邏輯分析儀能夠實時采集 FPGA 內(nèi)部信號,,幫助開發(fā)者觀察信號的時序與狀態(tài),。在調(diào)試數(shù)字電路設計時,,通過邏輯分析儀可查看信號的變化情況,,判斷邏輯設計是否符合預期,從而定位邏輯錯誤,。示波器可用于測量 FPGA 輸出的模擬信號或數(shù)字信號波形,,檢查信號的質量與完整性,如判斷信號是否存在畸變,、噪聲等問題,。此外,部分開發(fā)板配備板載調(diào)試器,,支持在線調(diào)試功能,,開發(fā)者可在不脫離開發(fā)板運行環(huán)境的情況下,進行斷點設置,、變量查看等操作,,快速定位軟件代碼中的問題,提高調(diào)試效率,,加速開發(fā)進程,。

在教育背景下,F(xiàn)PGA 開發(fā)板廣泛應用于創(chuàng)新教育課程,。學校開設 FPGA 相關課程,,培養(yǎng)學生硬件設計思維與創(chuàng)新實踐能力。學生在課程學習中,,不僅掌握電子技術基礎知識,,還通過實際操作開發(fā)板鍛煉解決問題能力。學校組織學生參加基于 FPGA 開發(fā)板的創(chuàng)新競賽,,激發(fā)學生創(chuàng)新熱情,,培養(yǎng)團隊協(xié)作精神。學生在競賽中運用所學知識,,設計開發(fā)具有創(chuàng)新性的作品,,如智能環(huán)保監(jiān)測裝置、創(chuàng)意電子藝術作品等,,提高學生綜合素質與創(chuàng)新能力,,為培養(yǎng)高素質創(chuàng)新型人才提供實踐平臺。電子競賽里,,F(xiàn)PGA 開發(fā)板憑借可編程優(yōu)勢,,成為選手制勝關鍵武器。

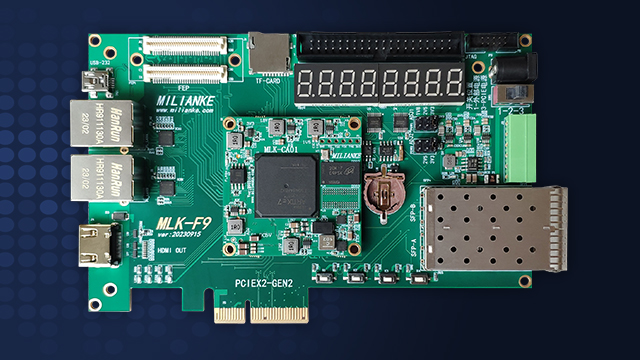

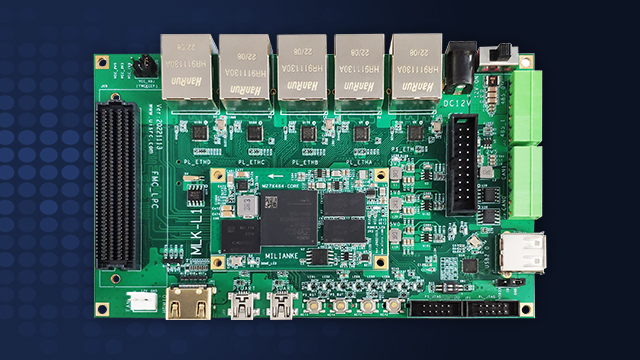

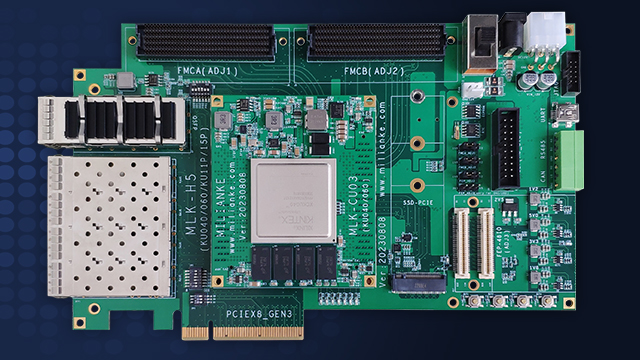

FPGA開發(fā)板是電子工程師與愛好者探索硬件世界的重要載體,,其硬件架構設計精巧且功能豐富,。以常見的XilinxZynq系列開發(fā)板為例,這類開發(fā)板集成了ARM處理器與FPGA可編程邏輯資源,形成獨特的異構架構,。ARM處理器部分可運行嵌入式操作系統(tǒng),,用于處理復雜的系統(tǒng)管理任務和軟件算法,,諸如文件系統(tǒng)管理、網(wǎng)絡通信協(xié)議棧運行等;而FPGA部分則可根據(jù)設計需求靈活構建各類數(shù)字電路,。開發(fā)板上還配備了豐富的存儲模塊,,包括用于程序存儲的Flash芯片,,能在斷電后長久保存系統(tǒng)啟動代碼與用戶程序,;以及用于數(shù)據(jù)緩存的DDR內(nèi)存,可在運行時存取大量數(shù)據(jù),。此外,,開發(fā)板設置多種通信接口,以太網(wǎng)接口方便連接網(wǎng)絡進行數(shù)據(jù)傳輸與遠程調(diào)試,,USB接口支持多種設備連接,,方便數(shù)據(jù)交互,SPI,、I2C等接口則用于連接各類傳感器與外設芯片,,為開發(fā)者搭建復雜硬件系統(tǒng)提供了充足的拓展空間。 FPGA 開發(fā)板的版本迭代,,帶來性能提升與功能增強,。重慶工控板FPGA開發(fā)板套件

FPGA 開發(fā)板的可重構特性,使其能快速適應不同項目需求的變化,。山東開發(fā)板FPGA開發(fā)板設計

FPGA開發(fā)板作為數(shù)字電路設計與驗證的重要載體,,其硬件架構設計融合了多種關鍵組件。開發(fā)板上的FPGA芯片是實現(xiàn)邏輯功能的器件,,不同型號的FPGA芯片在邏輯單元數(shù)量,、存儲資源、接口類型等方面存在差異,。以常見的入門級開發(fā)板為例,,往往搭載中低端FPGA芯片,能夠滿足初學者對基礎數(shù)字電路設計的實踐需求,。除了FPGA芯片,,開發(fā)板還配備電源管理模塊,該模塊通過多級電壓轉換,,為FPGA芯片及其他外設提供穩(wěn)定且適配的供電電壓,。例如,將外部輸入的5V電壓轉換為FPGA芯片所需的,、等工作電壓,。此外,,復位電路的存在確保開發(fā)板在啟動或異常情況下能恢復到預設狀態(tài),晶振電路則為整個系統(tǒng)提供精細的時鐘信號,,這些硬件組件協(xié)同工作,,構成了FPGA開發(fā)板穩(wěn)定運行的基礎。 山東開發(fā)板FPGA開發(fā)板設計

- 陜西學習FPGA開發(fā)板學習板 2025-06-24

- 定制FPGA定制項目學習視頻 2025-06-24

- 湖北了解FPGA開發(fā)板特點與應用 2025-06-24

- 廣東使用FPGA開發(fā)板資料下載 2025-06-24

- 河南開發(fā)板FPGA開發(fā)板資料下載 2025-06-24

- 上海嵌入式FPGA開發(fā)板交流 2025-06-23

- 安徽國產(chǎn)FPGA開發(fā)板套件 2025-06-23

- 陜西了解FPGA開發(fā)板入門 2025-06-23

- 福建ZYNQFPGA開發(fā)板工業(yè)模板 2025-06-23

- 四川工控板FPGA開發(fā)板套件 2025-06-23

- 化學蝕刻機公司 2025-06-24

- 福建57(CN)連接器廠家供應 2025-06-24

- 寧夏發(fā)光二極管銷售代理 2025-06-24

- 楊浦區(qū)進口配電開關報價 2025-06-24

- 高淳區(qū)哪里有集成電路芯片 2025-06-24

- 633 nm激光器費用 2025-06-24

- 蘇州電動叉車線束供應商 2025-06-24

- 河北攝像頭開發(fā)硬件開發(fā)費用是多少 2025-06-24

- 原廠原裝FDM32RV0049E-PQ64 2025-06-24

- 江蘇國產(chǎn)ESD二極管廠家 2025-06-24