荊門生產(chǎn)PCB制板價(jià)格大全

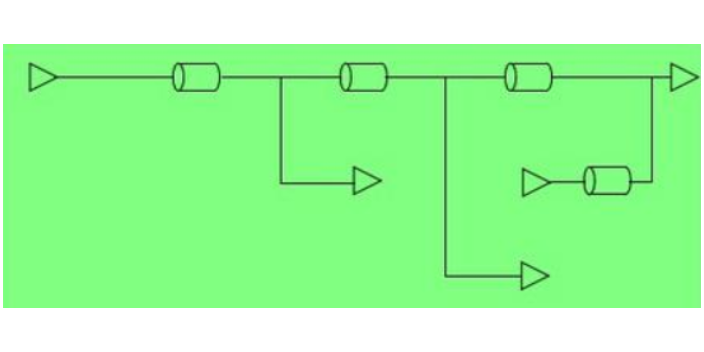

SDRAM的PCB布局布線要求1、對于數(shù)據(jù)信號,,如果32bit位寬數(shù)據(jù)總線中的低16位數(shù)據(jù)信號掛接其它緩沖器的情況,,SDRAM作為接收器即寫進(jìn)程時,首先要保證SDRAM接收端的信號完整性,,將SDRAM芯片放置在信號鏈路的遠(yuǎn)端,,對于地址及控制信號的也應(yīng)該如此處理。2,、對于掛了多片SDRAM芯片和其它器件的情況,,從信號完整性角度來考慮,SDRAM芯片集中緊湊布局,。3,、源端匹配電阻應(yīng)靠近輸出管腳放置,退耦電容靠近器件電源管腳放置,。4,、SDRAM的數(shù)據(jù),、地址線推薦采用菊花鏈布線線和遠(yuǎn)端分支方式布線,Stub線頭短,。5,、對于SDRAM總線,一般要對SDRAM的時鐘,、數(shù)據(jù),、地址及控制信號在源端要串聯(lián)上33歐姆或47歐姆的電阻;數(shù)據(jù)線串阻的位置可以通過SI仿真確定,。6,、對于時鐘信號采用∏型(RCR)濾波,走在內(nèi)層,,保證3W間距,。7、對于時鐘頻率在50MHz以下時一般在時序上沒有問題,,走線短,。8、對于時鐘頻率在100MHz以上數(shù)據(jù)線需要保證3W間距,。9,、對于電源的處理,SDRAM接口I/O供電電壓多是3.3V,,首先要保證SDRAM器件每個電源管腳有一個退耦電容,,每個SDRAM芯片有一兩個大的儲能電容,退耦電容要靠近電源管腳放置,,儲能大電容要靠近SDRAM器件放置,,注意電容扇出方式。10,、SDRAM的設(shè)計(jì)案列PCB制板技術(shù)工藝哪家好,?荊門生產(chǎn)PCB制板價(jià)格大全

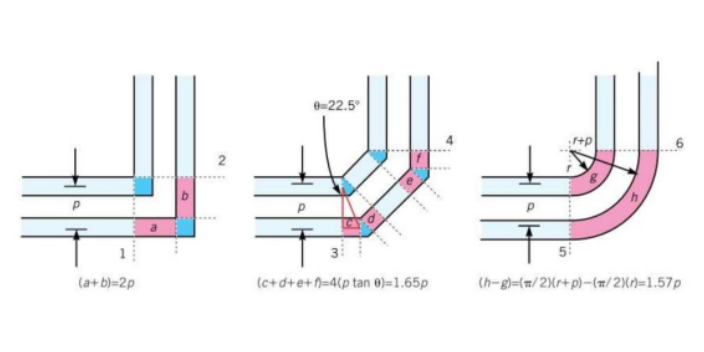

關(guān)鍵信號布線關(guān)鍵信號布線的順序:射頻信號→中頻、低頻信號→時鐘信號→高速信號,。關(guān)鍵信號的布線應(yīng)該遵循如下基本原則:一,、優(yōu)先選擇參考平面是地平面的信號層走線。二,、依照布局情況短布線,。三、走線間距單端線必須滿足3W以上,,差分線對間距必須滿足20Mil以上,。四、走線少打過孔,,優(yōu)先在過孔Stub短的布線層布線,。京曉科技可提供2-60層PCB設(shè)計(jì)服務(wù),,對HDI盲埋孔、工控醫(yī)療類,、高速通訊類,,消費(fèi)電子類,航空航天類,,電源板,,射頻板有豐富設(shè)計(jì)經(jīng)驗(yàn)。阻抗設(shè)計(jì),,疊層設(shè)計(jì),,生產(chǎn)制造,EQ確認(rèn)等問題,,一對一全程服務(wù),。京曉科技致力于提供高性價(jià)比的PCB產(chǎn)品服務(wù),打造從PCB設(shè)計(jì),、PCB生產(chǎn)到SMT貼片的一站式服務(wù)生態(tài)體,。湖北打造PCB制板批發(fā)同一塊PCB制板上的器件可以按其發(fā)熱量大小及散熱程度分區(qū)排列。

SDRAM的端接1,、時鐘采用∏型(RCR)濾波,,∏型濾波的布局要緊湊,布線時不要形成Stub,。2,、控制總線、地址總線采用在源端串接電阻或者直連,。3,、數(shù)據(jù)線有兩種端接方法,一種是在CPU和SDRAM中間串接電阻,,另一種是分別在CPU和SDRAM兩端串接電阻,,具體的情況可以根據(jù)仿真確定。京曉科技可提供2-60層PCB設(shè)計(jì)服務(wù),,對HDI盲埋孔、工控醫(yī)療類,、高速通訊類,消費(fèi)電子類,,航空航天類,,電源板,射頻板有豐富設(shè)計(jì)經(jīng)驗(yàn),。阻抗設(shè)計(jì),,疊層設(shè)計(jì),,生產(chǎn)制造,EQ確認(rèn)等問題,,一對一全程服務(wù),。京曉科技致力于提供高性價(jià)比的PCB產(chǎn)品服務(wù),打造從PCB設(shè)計(jì),、PCB生產(chǎn)到SMT貼片的一站式服務(wù)生態(tài)體,。

Cadence中X-net的添加1.打開PCB文件:(1).首先X-net是添加在串阻和串容上的一個模型,使得做等長的時候電阻或電容兩邊的網(wǎng)絡(luò)變成一個網(wǎng)絡(luò),,添加方法如下:1):找到串阻或者串容2):在Analyze->Modelassignment--點(diǎn)擊ok->點(diǎn)擊后跳出界面:用鼠標(biāo)直接點(diǎn)擊需要添加的電阻或者電容,;找到需要添加的器件之后點(diǎn)擊創(chuàng)建模型creatmodel之后彈出小框點(diǎn)擊ok--接下來彈出小框(在這里需要注意的是Value不能為零,如果是零歐姆的串阻請將參數(shù)改為任意數(shù)值)點(diǎn)擊--是--可以看到需要添加的串阻或串容后面出現(xiàn)--即X-net添加成功PCB制板可以起到穩(wěn)健的載體作用,。

扇孔推薦及缺陷做法左邊推薦做法可以在內(nèi)層兩孔之間過線,,參考平面也不會被割裂,反之右邊不推薦做法增加了走線難度,,也把參考平面割裂,,破壞平面完整性。同理,,這種扇孔方式也適用于打孔換層,。左邊平面割裂,無過線通道,,右邊平面完整,內(nèi)層多層過線,。京曉科技可提供2-60層PCB設(shè)計(jì)服務(wù),,對HDI盲埋孔、工控醫(yī)療類,、高速通訊類,,消費(fèi)電子類,航空航天類,,電源板,,射頻板有豐富設(shè)計(jì)經(jīng)驗(yàn)。阻抗設(shè)計(jì),,疊層設(shè)計(jì),,生產(chǎn)制造,EQ確認(rèn)等問題,,一對一全程服務(wù),。京曉科技致力于提供高性價(jià)比的PCB產(chǎn)品服務(wù),打造從PCB設(shè)計(jì),、PCB生產(chǎn)到SMT貼片的一站式服務(wù)生態(tài)體,。根據(jù)電路規(guī)模設(shè)置多層次PCB制板,。咸寧了解PCB制板

京曉科技PCB制板其原理、工藝流程具體是什么,?荊門生產(chǎn)PCB制板價(jià)格大全

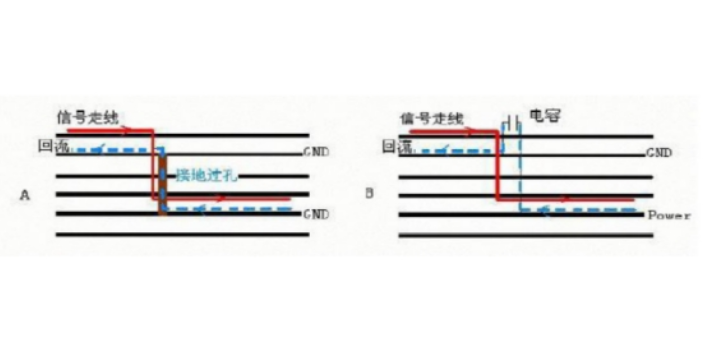

PCB制板EMI設(shè)計(jì)PCB設(shè)計(jì)中很常見的問題是信號線與地或電源交叉,,產(chǎn)生EMI。為了避免這個EMI問題,,我們來介紹一下PCB設(shè)計(jì)中EMI設(shè)計(jì)的標(biāo)準(zhǔn)步驟,。1.集成電路的電源處理確保每個IC的電源引腳都有一個0.1μf的去耦電容,對于BGA芯片,,BGA的四個角分別有8個0.1μF和0.01μF的電容,。特別注意在接線電源中添加濾波電容器,如VTT,。這不僅對穩(wěn)定性有影響,,對EMI也有很大影響。一般去耦電容還是需要遵循芯片廠商的要求,。2.時鐘線的處理1.建議先走時鐘線,。2.對于頻率大于或等于66M的時鐘線,每個過孔的數(shù)量不超過2個,,平均不超過1.5個,。3.對于頻率小于66M的時鐘線,每個過孔的數(shù)量不超過3個,,平均不超過2.5個,。4.對于長度超過12英寸的時鐘線,如果頻率大于20M,,過孔的數(shù)量不得超過2個,。5.如果時鐘線有過孔,在過孔附近的第二層(接地層)和第三層(電源層)之間增加一個旁路電容,,如圖2.5-1所示,,保證時鐘線改變后參考層(相鄰層)中高頻電流的回路的連續(xù)性。旁路電容所在的電源層必須是過孔經(jīng)過的電源層,,并且盡可能靠近過孔,,旁路電容與過孔的距離不超過300MIL。6.原則上所有時鐘線都不能跨島(跨分區(qū)),。荊門生產(chǎn)PCB制板價(jià)格大全

- 深圳常規(guī)PCB培訓(xùn)規(guī)范 2025-06-02

- 印制PCB制版多少錢 2025-06-02

- 湖北如何PCB培訓(xùn)廠家 2025-06-02

- 黃岡焊接PCB制版布線 2025-06-02

- 荊門常規(guī)PCB設(shè)計(jì)布線 2025-06-02

- 荊門焊接PCB制版原理 2025-06-02

- 打造PCB制版 2025-06-02

- 鄂州哪里的PCB設(shè)計(jì)加工 2025-06-02

- 專業(yè)PCB培訓(xùn)包括哪些 2025-06-02

- 荊州正規(guī)PCB制版布線 2025-06-02

- 杭州JVC攝像機(jī)光纜阻燃 2025-06-02

- 貴州鋰電池化成銷售價(jià)格 2025-06-02

- 遼寧進(jìn)口干式真空有載分接開關(guān) 2025-06-02

- 浙江厚膜光刻膠價(jià)格 2025-06-02

- 溫州磁懸浮傳輸線安裝 2025-06-02

- 中山全自動雕刻直流電機(jī)批發(fā)零售 2025-06-02

- 低壓車燈電子線 2025-06-02

- 智能化新能源線束售后服務(wù) 2025-06-02

- 惠州防靜電有機(jī)玻璃板 2025-06-02

- 金華電源濾波器作用 2025-06-02